ヒステリシス・コンパレータのしきい値を2Vと3Vにする抵抗値は?

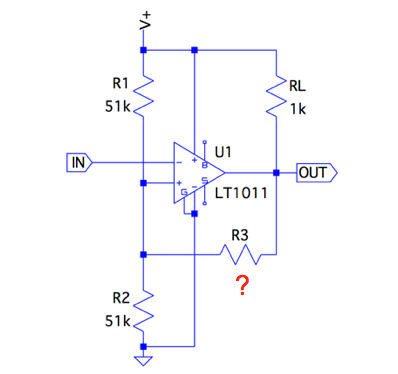

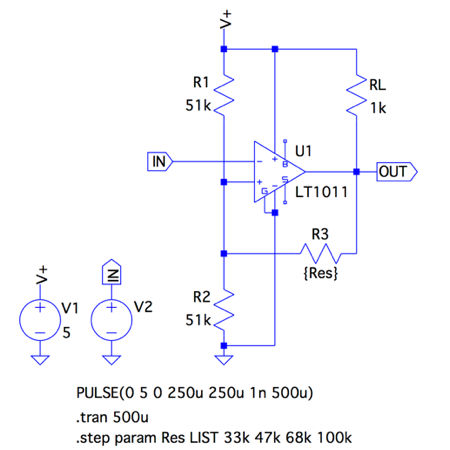

図1は,反転型のヒステリシス・コンパレータで,コンパレータ(LT1011)と四つの抵抗から構成されています.コンパレータの出力はオープン・コレクタで,回路の電源電圧(V+)が5V,抵抗(R1,R2)が51kΩ,負荷抵抗(RL)が1kΩです.この回路は,抵抗(R3)により,二つのしきい値電圧(VTH1,VTH2)があり,入力電圧はしきい値と比較され,出力電圧は反転したVOH,VOLとなります.

この回路で,しきい値VTH1が3V,VTH2が2Vとなる,R3の抵抗値は(a)~(d)のうちどれでしょうか.ここで計算を簡単にするためVOLを0Vとします.

コンパレータ(LT1011)のバランス入力(B)端子とストローブ入力(S)端子はオープンとしている.

図1は,非反転端子の電圧がしきい値となります.非反転端子と出力端子は正帰還となるR3で接続されており,しきい値は,出力電圧に関係します.二つの出力電圧(R3の右側)がHighまたはLowで比較し,それぞれの非反転端子のしきい値を計算すると求められます.オープン・コレクタ出力とは,NPNトランジスタのコレクタが,そのまま出力として端子に出ている出力形式のことです.

図1のヒステリシス・コンパレータは,非反転端子と出力端子がR3で正帰還されています.非反転端子のしきい値電圧は,二つの出力電圧の状態(High/Low)によって変わります.

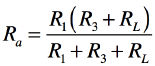

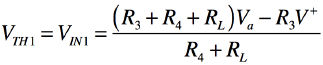

まず,出力がHighのときの非反転端子の電圧(VTH1)を求めます.この状態は,コンパレータ出力のオープン・コレクタがオフなので,「R3+RL」とR1の並列抵抗をRaとすれば,RaとR2からなる分圧回路の電圧が非反転端子に印加されます.Raは式1となり,非反転端子の電圧(VTH1)は式2となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

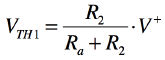

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

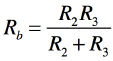

次に,出力がLowの状態の非反転端子の電圧(VTH2)を求めます.R3の右側はVOLが0Vなので,R2,R3の並列抵抗とR1からなる分圧回路の電圧が非反転端子に印加されます.R2とR3の並列抵抗をRbとすれば式3となり,非反転端子の電圧(VTH2)は式4となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

式2と式4へ図1の回路定数を使って,R3が33kΩ,47kΩ,68kΩ,100kΩのしきい値電圧を求めると次のようになります.

(a)33kΩ VTH1=3.6V,VTH2=1.4V

(b)47kΩ VTH1=3.4V,VTH2=1.6V

(c)68kΩ VTH1=3.2V,VTH2=1.8V

(d)100kΩ VTH1=3.0V,VTH2=2.0V

これより,しきい値電圧VTH1を3.0V,VTH2を2.0VとするR3は,(d)100kΩとなります.

●OPアンプとコンパレータの違いは出力段

OPアンプとコンパレータは,シンボルが三角形型で同じで,内部回路も初段の差動対,電流増幅段と構成が似ています.大きな違いは,出力段にあります.

OPアンプは,線形動作に重点においた設計になっていますが,コンパレータは,出力トランジスタが重い負荷(たくさん電流が流れる)でも飽和電圧が低く,高速でスイッチングするように設計されています.また,OPアンプは負帰還の補償のため内部にキャパシタがありますが,コンパレータにはありません.

コンパレータの出力は,大別すると二つあり,オープン・コレクタとトーテムポールです.オープン・コレクタは,負荷を接続して使い,出力トランジスタの耐圧の範囲内で,他の電源へ接続した負荷も扱えます.また,オープン・コレクタを複数接続してプルアップ抵抗を接続すると,ワイヤードOR回路が簡単に構成できます.トーテムポールは,外部の負荷抵抗が無くても動作します.

OPアンプとコンパレータの使われ方で比較すると,OPアンプは負帰還回路を構成してさまざまな回路機能を作ります.コンパレータはオープン・ループで動作させるデバイスであり,アナログ信号をデジタル信号へ変換する1bitのA-Dコンバータと考えることができます.

コンパレータに正帰還をかけるとヒステリシスをもたせることができます.ヒステリシスとは,入力電圧の往復路で,出力が切り替わるしきい値が違います.また正帰還を用いる別の利点は,出力電圧が変化すると,非反転端子と反転端子間の電圧差を増大させます.これは出力の遷移時間を速くします.

正帰還を使いヒステリシスを組み込む回路はOtto Schmitt氏によって考案され,シュミット・トリガ(Schmitt trigger)と呼ばれます.

●ヒステリシス・コンパレータについて

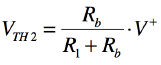

図2は(a)が反転型コンパレータ回路と(b)が反転型ヒステリシス・コンパレータ回路です.(a)と(b)の違いは正帰還抵抗のR3bの有無です.(b)は,図1と同じ回路です.まず,(a)の反転型コンパレータ回路から解説します.

二つの回路の違いは,正帰還抵抗R3bの有無

図2(a)の反転型コンパレータ回路は,非反転端子の電圧がしきい値(VTH)となり,反転端子へ印加された入力電圧はしきい値電圧と比較され,入力電圧と極性が反対のHighとLowの電圧(VOH,VOL)を出力します.LT1011の出力はオープン・コレクタですので,出力がHighのときは,コンパレータの出力は電流を吸い込まず,ハイ・インピーダンスとなります.したがって,出力電圧はV+の電圧となります.次に出力がLowのときは,オープン・コレクタは電流を吸い込み,NPNトランジスタの飽和電圧まで下がります.

以上の動作より,図2(a)は「V+=5V」とすれば,非反転端子の「VTH=2.5V」がしきい値となり,比較された2値の出力は「VOH=5V」,「VOL=NPNの飽和電圧」となります.NPNの飽和電圧は数百mVですので,ここでは「VOL=0V」とします.

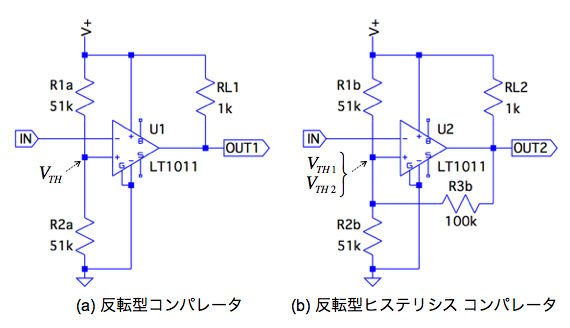

しきい値が一定のコンパレータは,入力信号に雑音が重畳されると誤動作する欠点があります.この様子を図3に示します.図3(a)が雑音が重畳された信号で,図3(b)が反転型コンパレータの出力波形,図3(c)がヒステリシス・コンパレータの出力波形です.

しきい値が一定のコンパレータの出力波形は誤動作し,ヒステリシス・コンパレータの出力は誤動作しない.

しきい値を境に重畳された雑音が振れると,出力もHigh/Lowを繰り返し,誤動作している様子がわかります.このような場合,ヒステリシス・コンパレータを使って雑音による誤動作を防ぎます.

図2(b)は正帰還となるR3bを加え,しきい値にVTH1,VTH2のヒステリシスを持たせた反転型のヒステリシス・コンパレータです.雑音が重畳された信号でも,最初に出力が切り替わったとき,しきい値を変えることにより誤動作を防ぎます.図3(c)がヒステリシス・コンパレータの出力です.このように,しきい値にヒステリシスを持たせると,雑音が重畳された信号でも誤動作しません.

●反転型ヒステリシス・コンパレータをLTspiceで確かめる

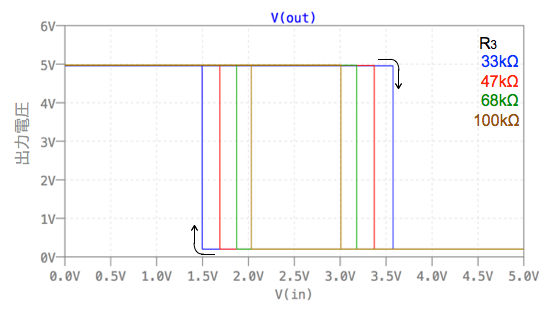

図4は,図1をシミュレーションする回路です.電源電圧が5Vで,入力信号の振幅が0Vから5V,立ち上がり時間と立ち下がり時間を250μsの三角波で過渡解析を行います.また,R3は「.stepコマンド」で33kΩ,47kΩ,68kΩ,100kΩを切り替えました.

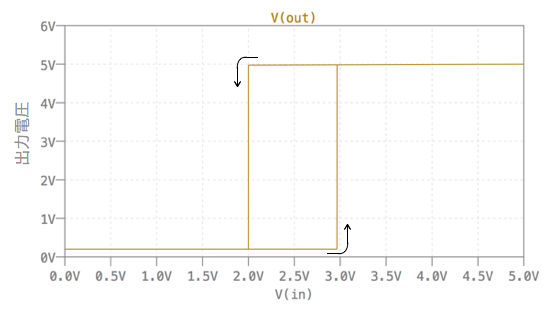

図5は,図4のシミュレーション結果です.横軸は入力電圧,縦軸は出力電圧をプロットしました.解答のR3が100kΩのとき,出力電圧が切り替わる入力電圧をカーソルで調べると,VTH1が3.01V,VTH2が2.03Vです.解答の計算とシミュレーションで僅かに誤差があるのは,オープン・コレクタの飽和電圧を「VOL=0V」で計算したことによります.

過渡解析の結果を使い,横軸は入力電圧へ変更した.

●非反転型ヒステリシス・コンパレータ

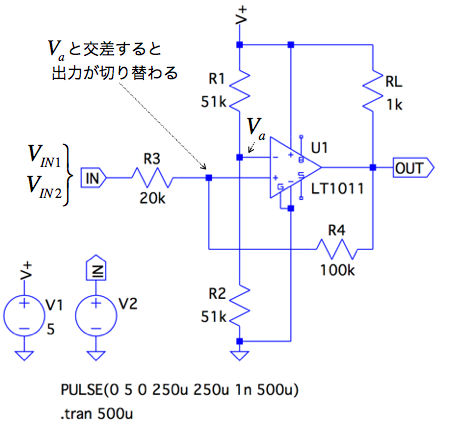

図6は,非反転型ヒステリシス・コンパレータで,反転型と比べると抵抗が1個増えます.非反転型ヒステリシス・コンパレータは,反転端子へ固定の電圧を印加し,入力側のR3とR4により,非反転端子の電圧を出力電圧によって切り替えることにより,ヒステリシス特性をもたせています.

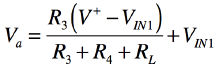

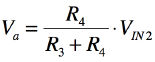

R1とR2の分圧回路からコンパレータの反転端子へ印加する電圧をVaとし,出力のHigh/Lowによって切り替わる,非反転端子の出力電圧を調べます.出力がHighのとき,非反転端子の電圧が反転端子の電圧Vaと交差して,出力が切り替わる入力電圧をVIN1とすると,式5が成り立ちます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

出力が切り替わるときの入力電圧がしきい値ですので,式5をVIN1で整理すると,式6となります.

・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・(6)

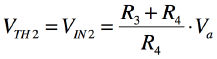

次に出力がLowのとき,非反転端子の電圧が反転端子のVaと交差し,出力が切り替わる入力電圧をVIN2とすると,式7が成り立ちます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)

このときの入力電圧が,もう一つのしきい値であり,式7をVIN2で整理すると,式8となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(8)

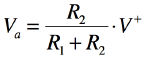

ここで,Vaは式9です.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(9)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(9)

式6と式8より,図6の回路定数を使って計算すると,二つのしきい値は,「VTH1=2.0V」,「VTH2=3.0V」と求められます.

図7は,図6のシミュレーション結果です.二つのしきい値をカーソルで調べると「VTH1=2.00V」,「VTH2=2.95V」であり,シミュレーションと手計算は,ほぼ合っていることが確認できます.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice2_032.zip

●データ・ファイル内容

Hysteresis_comparator1.asc:図4の回路

Hysteresis_comparator2.asc:図6の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs