ひずみの小さい電流ブースタ・アンプはどっち?

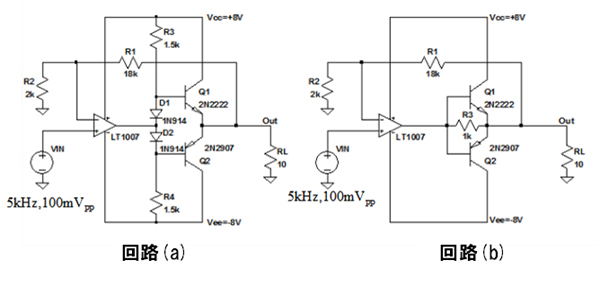

図1の回路(a)と(b)は,OPアンプの出力電流能力を上げるために,NPNとPNPトランジスタによるプッシュプル・エミッタ・フォロワを追加した電流ブースタ・アンプです.回路(a)と(b)は,どちらも電源電圧が±8Vで,ゲインが20dBに設定してあり,10Ωの負荷抵抗(RL)が接続されています.回路(a)と(b)の違いは,回路(a)のプッシュプル・エミッタ・フォロワには,抵抗(R3,R4)とダイオード(D1,D2)で構成したバイアス回路があります.

この両方の回路に5kHzで100mVPPの正弦波を加えた場合,出力のひずみが小さいのは,回路(a)と(b)のどちらでしょうか.

回路(a)のプッシュプル・エミッタ・フォロワには,抵抗(R3,R4)とダイオード(D1,D2)で構成した

バイアス回路がある.

回路(a)

回路(a)は,抵抗(R3,R4)とダイオード(D1,D2)で構成したバイアス回路が,トランジスタ(Q1,Q2)に常に電流が流れるように働き,クロスオーバひずみ(信号のゼロ・クロス付近のひずみ)が小さくなります.一方,回路(b)は,抵抗R3を入れることで,クロスオーバひずみの対策を行っていますが,負荷抵抗(RL)に対してR3の値が大きいので,ほとんど効果がありません.回路(b)は,オーディオ製品など,ひずみを考慮する製品には使用できません.従ってひずみが小さい回路は,回路(a)ということになります.

●OPアンプの出力電流能力

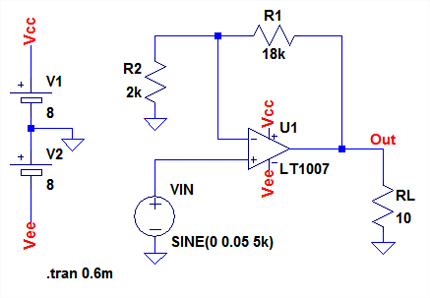

一般的なOPアンプはあまり大きな出力電流を流すことができません.品種にもよりますが,最大電流は20mA~30mA程度です.図2は,回路(a)と(b)のOPアンプだけの出力電流を確認する回路です.OPアンプ(LT1007)を使って,ゲインを20dBに設定し,10Ωの負荷抵抗(RL)を接続し,5kHzで100mVPPの正弦波を加えた,シミュレーション用の回路です.

10Ωの負荷抵抗が接続されている.

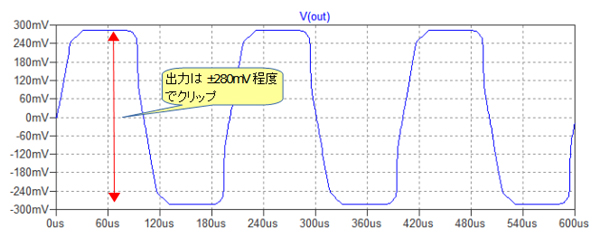

図3は,図2のシミュレーション結果です.出力電圧は,±280mV程度でクリップしています.負荷抵抗(RL)が10Ωですから,出力電圧を10Ωで割った,±28mAが,このOPアンプが出力できる最大の電流ということになります.

出力は±280mV程度でクリップしている.

●OPアンプの出力電流能力を増強する

負荷抵抗(RL)が小さくても,きちんと出力電圧を出せるようにするには,OPアンプの出力電流能力を強化する必要があります.このようなときに,使われるのが,図1の回路(a)と(b)のようなトランジスタを使用した電流ブースタ回路です.

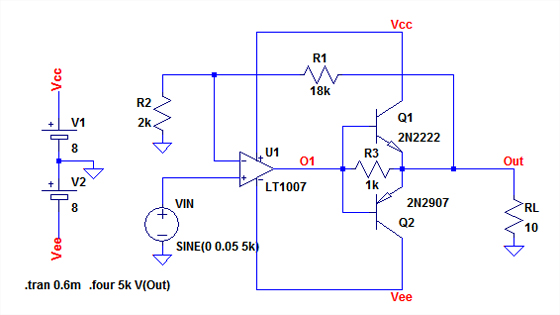

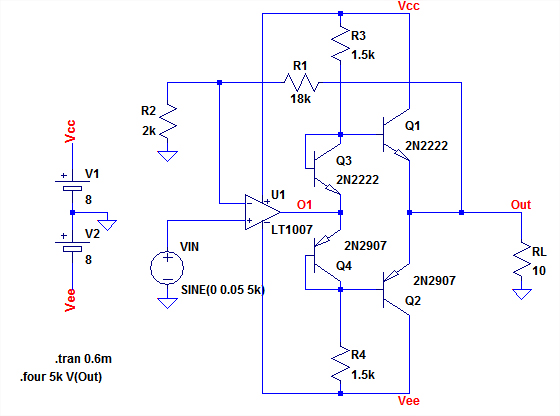

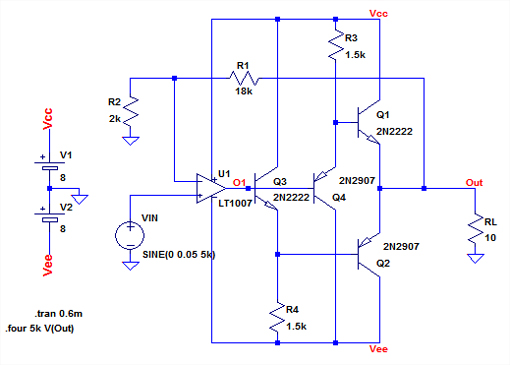

図4は,回路(b)をシミュレーションするための回路です.NPNトランジスタQ1は,出力信号がプラス側に振れたときにエミッタ・フォロワとして働き,PNPトランジスタQ2は,マイナス側に振れたときにエミッタフォロワとして働きます.このような回路をプッシュプル・エミッタ・フォロワと呼んでいます.

OPアンプにプッシュプル・エミッタ・フォロワが追加されている.

ここで重要なのが,帰還抵抗R1の接続位置です.R1をOPアンプ出力ではなく,トランジスタのエミッタとすることで,Q1とQ2が負帰還(NF)ループ内に入り,トランジスタで発生するひずみを低減することができます.ただし,このひずみ低減効果にも限界があり,ゼロ・クロス付近の波形ひずみに関しては十分に低減することができません.信号周波数が高いほど,このゼロ・クロス付近のひずみが目立つようになります.ゼロ・クロスとは,Q1とQ2が波形のプラス側とマイナス側を分担しているので,切り替わるつぎ目を指します.

●クロスオーバひずみの原因

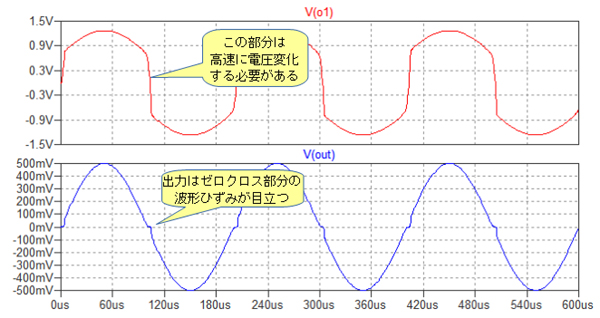

図5は,図4のシミュレーション結果です.図5下段は,出力電圧(OUT端子)の波形です.ゼロ・クロス付近で波形が階段状にひずんでいることがわかります.これは,ゼロ・クロス付近で,波形のプラス側とマイナス側でトランジスタQ1とQ2がなめらかに切り替わる必要がありますが,OPアンプ出力の電圧変化が十分に高速変化しておらず,うまく切り替わっていないためです.

クロスオーバひずみは,ゼロ・クロス付近で,トランジスタQ1とQ2が動作しないために発生します.そこで,R3は,トランジスタQ1とQ2が動作しないときに,OPアンプが直接,負荷抵抗(RL)を駆動するために配置しました.要するに,R3は,クロスオーバひずみを低減する目的で配置しています.しかし,負荷抵抗(RL)が小さい場合,OPアンプ出力は,R3と負荷抵抗(RL)で分圧されます.そのため,十分に負荷抵抗(RL)を駆動することができないため,R3の効果がありません.

ゼロ・クロス付近の波形ひずみが目立つ.

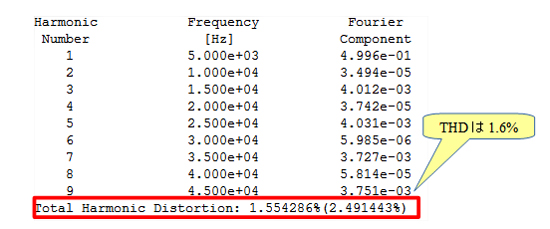

表1は,図4の回路のフーリエ解析の結果です.フーリエ解析の結果はCTRL+Eでエラーログを表示することで確認できます.THD(Total Harmonic Distortion)は約1.6%と悪い結果となっています.

THDは約1.6%.

●回路(b)のR3の値を変更して確認する

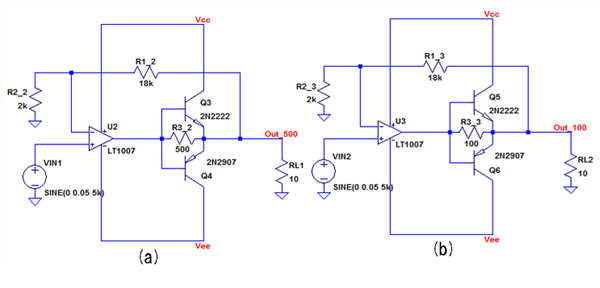

図6(a)(b)は,回路(b)の抵抗R3の値(1KΩ)を変更し,シミュレーションするための回路です.図6(a)は500Ω,図6(b)は100Ωに変更しています.

図6(a)は500Ω,図6(b)は100Ωに変更している.

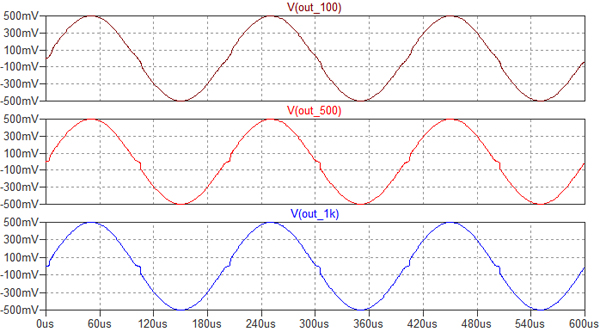

図7は,図6(a)(b)と回路(b)の電圧出力波形です.図7上段が図6(b)のR3を100Ωにした出力波形で,図7中段が図6(a)のR3を500Ωにした出力波形です.図7下段は,比較するために回路(b)の出力波形(図5下段と同じ)を並べました.

図7上段が100Ωの出力波形,図7中段が500Ωの出力波形,図7下段が1KΩの出力波形.

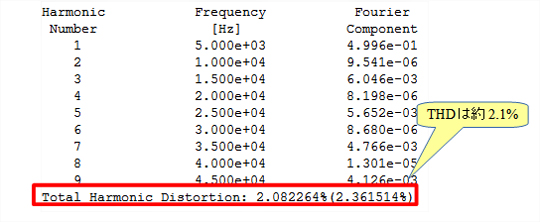

図7上段(100Ω)を見るとゼロクロス付近の階段状の波形は,多少なめらかになっています.しかし,表2の図6(b)のR3を100Ωにしたときのフーリエ解析の結果を見ると,THDは約2.1%と表1よりさらに悪くなっています.図1の回路(b)は,定数の変更をしてもひずみを改善するのは難しいことがわかりました.これは,抵抗R3の負荷が小さくなることにより,OPアンプに流れる電流が増えて,OPアンプの負担が大きくなったからです.

THDは約2.1%.

●クロスオーバひずみの小さな回路を確認する

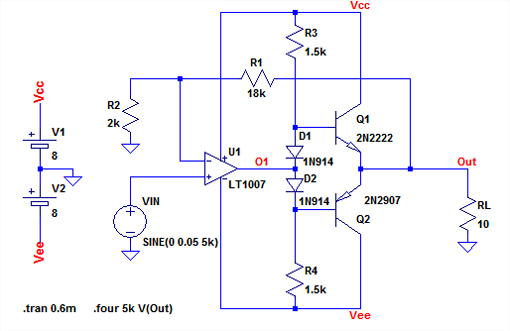

図8は,回路(a)をシミュレーションするための回路です.プッシュプル・エミッタ・フォロワには,抵抗(R3,R4)とダイオード(D1,D2)で構成したバイアス回路があります.

抵抗(R3,R4)とダイオード(D1,D2)で構成したバイアス回路がある.

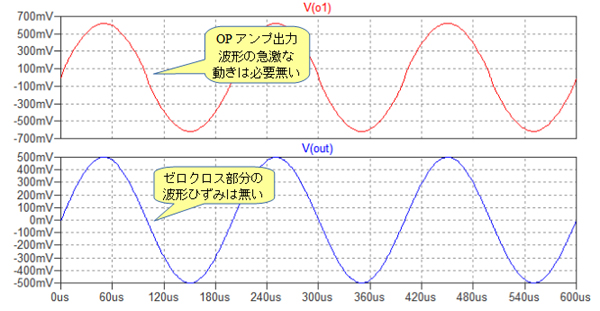

図9が,図8のシミュレーション結果となります.図9下段が出力電圧波形ですが,図5のようなゼロ・クロス付近の波形のひずみはありません.また,図9上段はOPアンプ出力ですが,ダイオード(D1,D2)があることにより,トランジスタ(Q1,Q2)に常に一定のバイアス電圧が与えられ,トランジスタがなめらかに切り替わり,OPアンプ出力は,ゼロ・クロス付近で急速に変化する必要がありません.

図5のようなゼロ・クロス付近のひずみが無い.

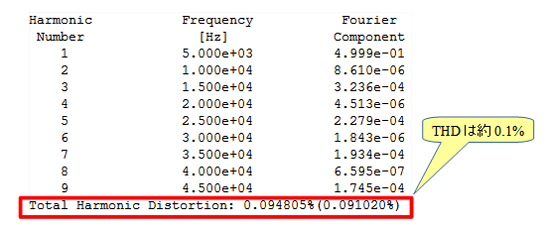

表3は,図8の回路のフーリエ解析の結果です.THDは,約0.1%と図4の回路よりも一桁以上小さくなり良くなっています.

THDは約0.1%.

●トランジスタのベース電流を充分供給できる値にする

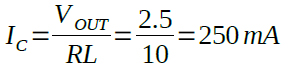

図8の抵抗(R3,R4)は,トランジスタ(Q1,Q2)のベース電流を充分供給できるような値にする必要があります.図8の回路の最大出力電圧を2.5V(ピーク値)とすると,Q1のコレクタ電流は式1のように250mAになります.

・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・(1)

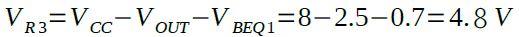

Q1の電流増幅率(hfe)を100とすると,必要なベース電流は2.5mAです.一方,そのときに抵抗R3に加わっている電圧は,式2のように4.8Vです.

・・・・・・・(2)

・・・・・・・(2)

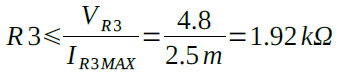

そして,R3が供給できる最大電流(IR3MAX)を2.5mA以上とするためにはR3は式3のように,1.92kΩ以下とすれば良いことになります.

・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・(3)

●その他の電流ブースタ回路

最後に,プッシュプル・エミッタ・フォロワを使用した電流ブースタは,他の回路構成もあります.図10は,図8のダイオードの代わりにベース・コレクタをショートさせたトランジスタに置き換えた回路です.無信号時にトランジスタ(Q1,Q2)に流れる電流が計算しやすいというメリットがあります.

図11のような,ダイオード接続のトランジスタをエミッタ・フォロアに置き換えた回路もよく使用されます.図11の回路に関しては,「004 トランジスタの発熱 が大きいのはどっち? 2014年9月26日配信」を参考にしてください.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice040.zip

●データ・ファイル内容

OPamp.asc:図2の回路

current_Boost_B.asc:図4の回路

current_Boost_B_R3.asc:図6の回路

current_Boost_A.asc:図8の回路

current_Boost_A_2.asc:図10の回路

current_Boost_A_3.asc:図11の回路

※ファイルは同じフォルダに保存して,フォルダ名を半角英数にしてください

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs