ひずみ率の小さいエミッタ接地アンプはどっち?

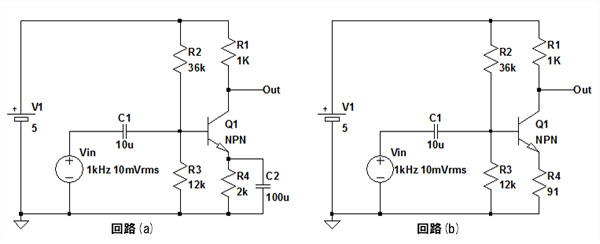

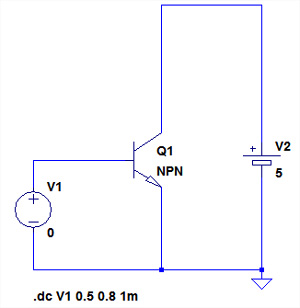

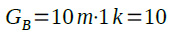

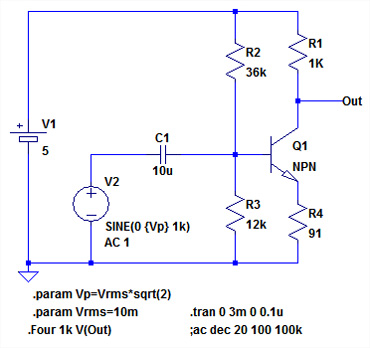

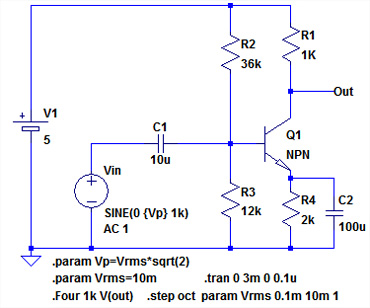

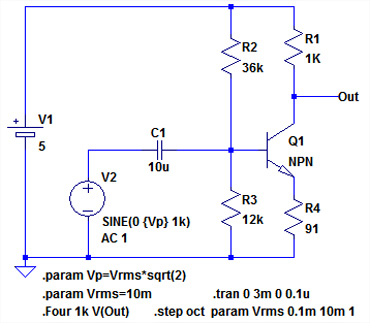

図1の回路(a)と(b)ともにゲイン20dBとなるように定数が設定されたエミッタ接地アンプです.両者の違いは,抵抗R4の大きさとエミッタ・バイパス・コンデンサ(C2)の有無です.この二つのアンプに1kHzで10mVrmsの正弦波を加えた時,出力波形のひずみ率(THD:Total Harmonic Distortion)が小さい(正弦波に近い)のはどちらでしょうか.

回路(a)は,バイパス・コンデンサ(C2)があるエミッタ接地アンプ回路.回路(b)は,バイパス・コンデンサ無しのエミッタ接地アンプ

●エミッタ接地回路

トランジスタを使用した増幅回路には基本として,エミッタ接地回路,コレクタ接地回路,ベース接地回路の三種類の回路があります.エミッタ接地回路は,その中でもよく使用される回路です.

回路(b)

回路(b)のアンプはエミッタに接続された抵抗R4によって電圧と電流変換のリニアリティが改善され,回路(a)のアンプよりもTHDが小さくなります.

●エミッタ接地増幅回路のゲインの設定

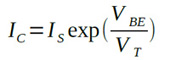

まず,エミッタ接地増幅回路のゲインをどのように計算するのか解説します.トランジスタのベース・エミッタ間電圧(VBE)とコレクタ電流(IC)の特性は式1で表すことができます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

ただし

IS:逆方向飽和電流,k:ボルツマン定数,T:絶対温度,q:電子電荷

IS:逆方向飽和電流,k:ボルツマン定数,T:絶対温度,q:電子電荷

交流ゲインを求めるためには,VBEが微小に変化した時(ΔVBE)のICの変化量を知る必要があります.このΔVBEに対するICの変化率が相互コンダクタンス(gm)です.つまり,式1をVBEで微分したものがgm(式2)になります.

・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・(2)

また,交流等価抵抗reはgmの逆数なので,式3で示されます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

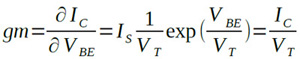

●トランジスタのVBEとICの特性を検証

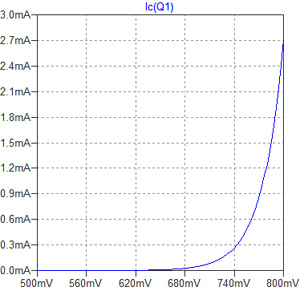

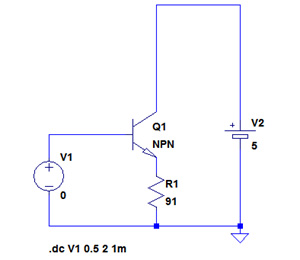

図2は,式1と式2を検証するためにLTspiceで作成した回路です.トランジスタのVBEを変えた時に,ICがどのように変化するかをシミュレーションします.

トランジスタのVBEを変えた時に,ICがどのように変化するか確認する

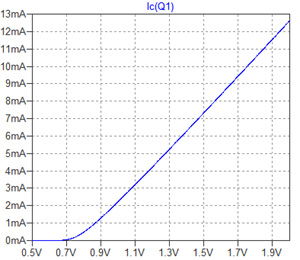

図3は,図2のシミュレーション結果です.図3は,式1をグラフにしたものと同等のグラフになります.gmを表示させるには,図3の上部「IC(Q1)」を右クリックして,「d(IC(Q1))」に書き換えます.これはIC(Q1)を横軸(V1)で微分するという意味です.

式1をグラフにしたものと同等のグラフになる

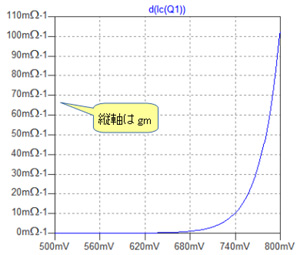

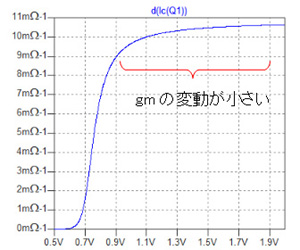

図4は,図3のIC(Q1)を横軸(V1)で微分して,縦軸をgmとして表示させた,V1(VBE)対gmのグラフです.グラフの縦軸がgmで,単位はΩ-1となっていますが,gmの単位としてはS(ジーメンス)がよく使用されます.

gmの単位としてはS(ジーメンス)がよく使用される

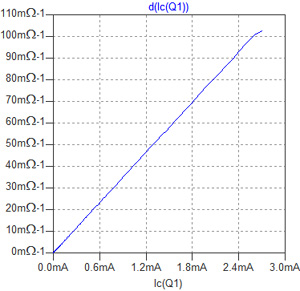

さらに,図4の横軸をクリックし,表示されたダイアログ中のV1を「IC(Q1)」に書き換えて,横軸を「IC(Q1)」として表示したものが図5です.これは,ICによってgmがどのように変化するのかを表しています.式2より,gmはICに比例することがわかりますが,図5からもそれを知ることができます.

ICによってgmがどのように変化するのかを表示

●エミッタ接地増幅回路のゲインを表す式

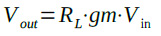

回路(a)と(b)の抵抗R1を負荷抵抗(RL)とすると,入力にVinという微小信号が加えられた時の出力電圧Voutは,式4で計算できます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

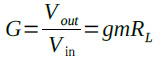

ゲインGは,出力電圧を入力電圧で割ったものなので,式5になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

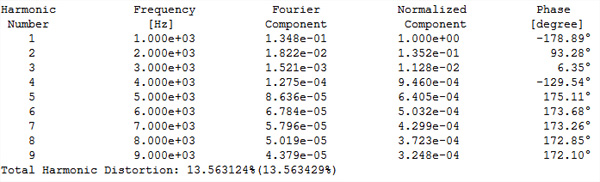

式5が,エミッタ接地増幅回路のゲインを表す式になります.次に,負荷抵抗1kΩでゲインを20dB(10倍)とするのに必要なgmは,式5を使用し,式6のように求められます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

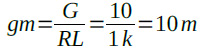

さらに,gmを10mSにするためにトランジスタに流すべき電流(IC)は,式2を式7のように変形することにより,計算することができます.

・・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・・(7)

つまり,トランジスタのICが260μAになるようにバイアス回路を組めばよいのです.しかし,ゲインを安定に設定するためには,ICが温度や電源電圧で変化しにくいようにする必要があります.

●回路(a)のエミッタ接地増幅回路のゲインの設定

回路(a)では,バイアス回路として,電源電圧をR2とR3の抵抗で分圧したものでベース電圧を設定し,さらにR4をエミッタに入れることで,温度や電源電圧によるICの変化を小さくしています.そのうえで,R4にコンデンサC2を並列に接続し,交流的にR4をショートしたものとみなすことができるようにしています.これにより,回路(a)のgmの計算には,式2がそのまま使用できます.回路(a)では,ベース電圧を約1.2VになるようにR2,R3の分圧比を設定し,R4を2kΩとすることで,式7どおりに,ICがおおよそ260uAになるようにして,ゲインを20dBに設定しています.

●回路(b)のエミッタ接地増幅回路のゲインの設定

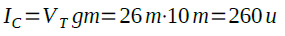

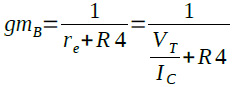

回路(b)では,コンデンサC2を接続しないかわりに,トランジスタの電流を増やし,R4を小さくしています.回路(b)のICに対する交流等価抵抗は,トランジスタのreとR4を足したものになり,gmは式8のように,reとR4の逆数になります.

・・・・・・・・・・・・・・・・・・・・・・・・・・(8)

・・・・・・・・・・・・・・・・・・・・・・・・・・(8)

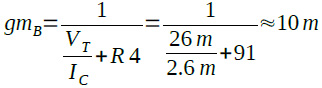

式8より,R4があることによって,回路(b)はICの変動によるgmの変化を小さくできることがわかります.ここで,回路(b)のgmとV1の関係をシミュレーションで確認してみます.図6がシミュレーションのための回路図です.図7は,図6のV1対ICのカーブを示しました.

図8は図7をV1で微分したgmのカーブです.図8を見るとわかるように,0.9VよりもV1が大きい領域では,V1によるgmの変動が小さくなっていることがわかります.gmの変動が小さいということは,入力電圧を電流に変換する時のリニアリティが良く,ひずみが少ないことを表しています.

回路(b)のICは,約2.6mAとなるよう設定してあります.式8に数値を代入するとgmは式9のように約10mSとなります.

・・・・・・・・・・・・・・・・・・・・・(9)

・・・・・・・・・・・・・・・・・・・・・(9)

また,ゲインは式10により,回路(a)と同様20dBとなることがわかります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(10)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(10)

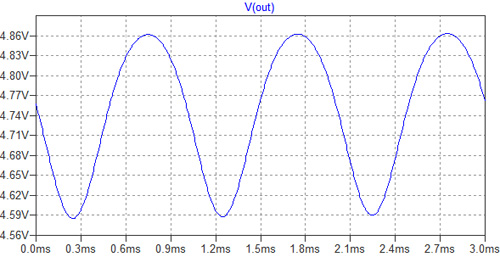

●回路(a)の10mVrms入力の時THDをシミュレーションする

回路(a)と(b)ともに,ゲインが20dBとなることが確認できたので,10mVrms入力の時の出力のTHDをシミュレーションしてみます.まず,実効値で入力の振幅を指定するため,二つの変数を定義します.実効値を表すVrmsを「.param Vrms=10m」として定義します.次にピーク値のVpを「.param Vp=Vrms*sqrt(2)」として定義します.トランジェント解析は,「.tran 0 3m 0 0.1u」のように,最少刻み幅を指定します.この指定は無くても解析は可能ですが,THDの解析精度がかなり悪くなってしまいます.また,「.Four 1k V(out)」というコマンドでTHDを出力させます.

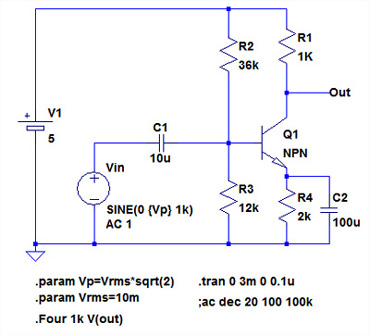

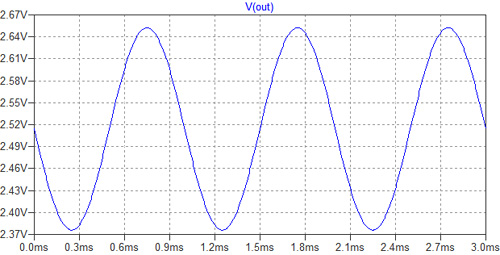

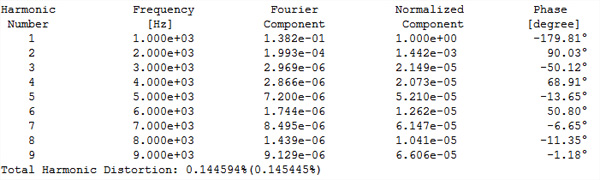

図9がシミュレーション用の回路図です.図10がその出力波形となります.THDは,「Ctrl+E」キーを押して解析ログを表示させ確認します.表1がその結果です.THDは,13.6%とかなり悪い値となっています.

●回路(b)の10mVrms入力の時THDをシミュレーションする

回路(b)でも回路(a)と同様にシミュレーションしてみます.図11が回路(b)のシミュレーション用回路図で,図12がその出力波形です.表2が「.Four」解析出力結果です.図12の出力波形は,回路(a)の図10と比較して明らかに正弦波に近く,「.Four」解析のTHDも0.15%とかなり良い結果となっています.

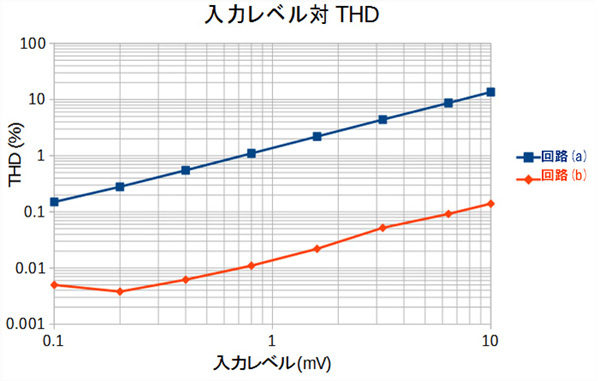

●入力レベルとひずみの関係をシミュレーションで確認する

次に入力レベルによるTHDの変化をシミュレーションしてみます.図13は,図9の回路に,「.step」コマンドの「.step oct param Vrms 0.1m 10m 1」を追加したものです.このコマンドは,Vrmsというパラメータの値を,1オクターブあたり1ポイントの割合で0.1mから10mまで変化させて解析する,という意味になります.つまり,入力レベルを0.1mVrmsから10mVrmsまで,倍々に増やしてトランジェント解析を実行します.

図14は,図11の回路に図13と同じように「.step」コマンドを追加したものです.

図15は,図13と図14の回路でシミュレーションを実行し,「Ctrl+E」キーを押して表示した,解析ログの中の「.Four」解析の結果から,THDを読み取り,表計算ソフトでグラフにまとめたものです.明らかに回路(b)のほうがひずみ特性が良好であることがわかります.

明らかに回路(b)のほうがひずみ特性が良好である

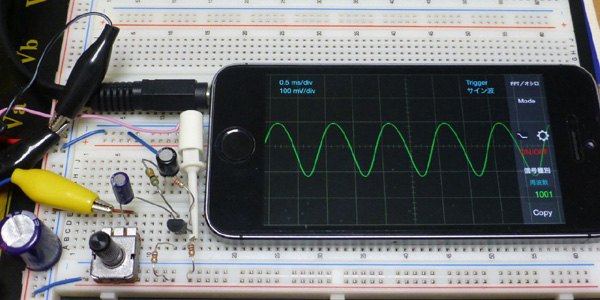

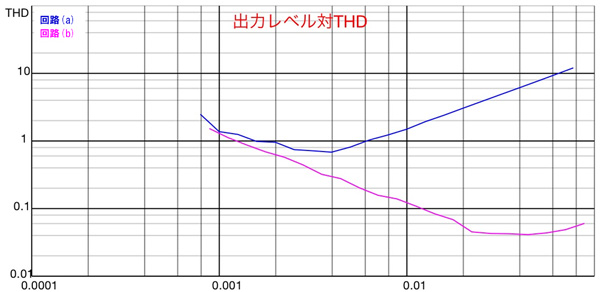

●実際の回路で実測した結果

最後に,参考として回路(a)と(b)をトランジスタ「2SC1815」を使用して実際に回路を組み(写真1),実測した結果を図16に示します.電流値を合わせるため,抵抗R3は10kΩに変更しています.

測定にはiPhoneとe-scope3-in1というアプリを使用

なお,測定にはe-scope3-in-1というiPhone・iPad用のアプリを使用しています.測定データの絶対値は,校正されたものではありませんが,今回のように性能の相対比較をする場合は,簡単にひずみデータを取得することができます.出力レベルが低い時に,シミュレーションに比べてTHDが大きくなっていますが,これはノイズの影響です.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice022.zip

●データ・ファイル内容

Ic_Vbe.asc:図2の回路

Ic_Vbe_B.asc:図6の回路

amp_A_1.asc:図9の回路

amp_B_1.asc:図11の回路

amp_A_2.asc:図13の回路

amp_B_2.asc:図14の回路

※ファイルは同じフォルダに保存して,フォルダ名を半角英数にしてください

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs