ボルテージ・フォロワで発振が止まる回路はどっち?

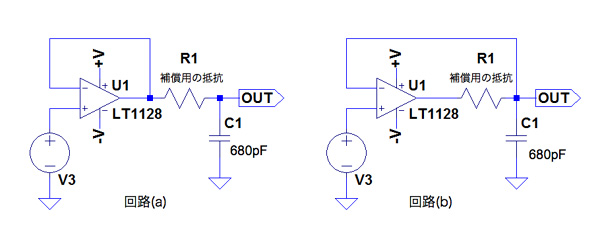

図1は,OPアンプ(LT1128)とコンデンサ(C1: 680pF) で構成したボルテージ・フォロワ回路です.ボルテージ・フォロワ回路は,負荷容量のC1が接続されると発振しやすくなるため,発振を抑える目的で,補償用の抵抗(R1)を回路(a)と(b)のように追加しました.非反転端子へ矩形波を入力した場合,どちらの回路で発振が止まるでしょうか?

回路(a)

図2は,回路(a)と(b)の回路網を示しています.OPアンプの開ループ周波数特性をA(s),OPアンプ内の出力抵抗(Ro)を分かりやすいようにOPアンプ・シンボルの外へ図示しています.ループ・ゲインと位相周波数特性は,ループ入力からループ出力まで負帰還を一巡したものです.

回路(a)は,ループ出力端子からグラウンド(GND)へR1とC1が直列になっています.この直列接続はループ・ゲインと位相周波数特性にゼロ点を作り,R1を調節することにより位相を進ませ,発振を止める効果が見込めます.

一方,回路(b)のループ・ゲインと位相周波数特性は,RoとC1で決まるポールの周波数が,R1の追加分だけ低くなり,回路(a)のような効果は見込めません.

回路(a)は負荷のR1,C1でゼロ点を作る

●ボルテージ・フォロワ回路は,負荷容量が追加すると発振しやすい

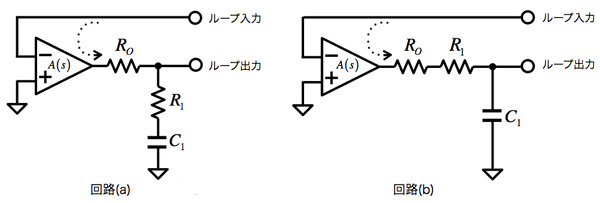

はじめに,ボルテージ・フォロワ回路に負荷容量(C1)が無い場合と有る場合でどのように変化するのか見てみます.図3は,回路(a)と(b)の補償用の抵抗(R)を外した回路です.非反転端子へ図3で示すように,矩形波を入力します.

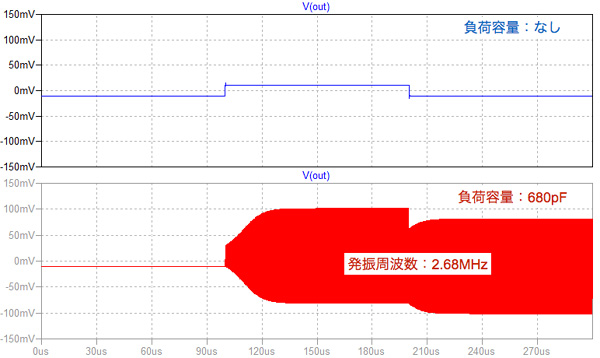

C1が無い場合と有る場合で過渡解析を行いました.図4に示すとおり負荷容量が無い場合は負帰還は安定し,負荷容量が有る場合は不安定になり発振しやすくなります.

負荷容量が無いと発振せず,負荷容量が有ると発振している

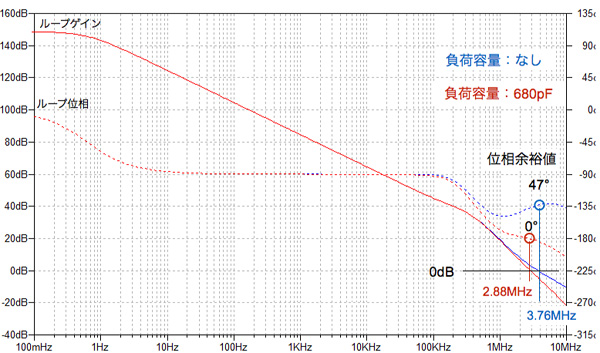

図5は図3の回路で負荷容量の有無で,ループ・ゲインと位相周波数特性を調べた結果です.負荷容量が680pFのとき位相余裕が0°という結果になりました.

負荷容量がない状態で位相余裕は47°,負荷容量が680pFでは位相余裕0°の様子

●middlebrook法と過渡解析

ボルテージ・フォロワ回路は帰還率が1で,クローズ・ループ・ゲインを大きくした負帰還回路より不安定です.これに負荷容量を接続すると新たなポールが増え,この位相遅れによって更に不安定となり出力が発振することがあります.回路(a)は,ボルテージ・フォロワ回路の出力と負荷容量の間に直列にR1を追加し負帰還の安定性補償をします.欠点は,ボルテージ・フォロワ回路から後段に流れる負荷電流とR1で発生する電圧降下です.この電圧降下が本来要求されている回路特性に影響を与えなければ,R1だけで発振を抑制できます.

今回は実際の回路設計に近い例として,リニアテクノロジー社のOPアンプ「LT1128」のマクロモデルを用いて過渡解析で発振を確認します.過渡解析は,時間で変化する特性について解析を行います.また,理論的に誤差のない測定手法のmiddlebrook法を用いたループ・ゲインと位相周波数特性でR1の効果を確かめ,過渡解析において発振が停止する様子を確認していきます.

●RC回路の特性

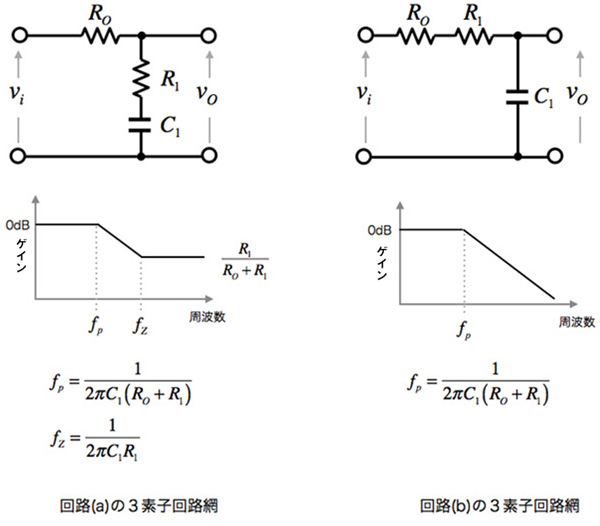

図6は,回路(a)と(b)のRo,R1,C1からなる3素子回路網の特性を調べたものです.RoはOPアンプの出力抵抗,R1は補償用抵抗,C1は負荷容量です.図6の中には3素子回路網の回路図と,そのボード線図を示しました.

図6の回路(a)の3素子回路網のゲイン・ボード線図は,直流に近い低周波ではゲインは0dB(1倍),低い周波数側にポール(fp)があり,fpとゼロ点(fz)の間は,-20dB/decの傾きで減衰し,高周波になるとゲインの減衰が止まりRoとR1の抵抗比で決まります.ループ・ゲインと位相周波数特性が不安定になる原因は負荷容量による新たなポールの存在であり,それを式3のゼロ点を使った補償が期待できます.

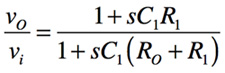

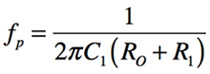

回路(a)の3素子回路網の伝達関数は式1で表せます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

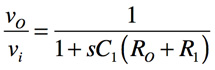

式1はC1とRo+R1のポール(fp),またC1とR1のゼロ点(fz)があり,それぞれ式2,式3です.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

回路(b)の3素子回路網の伝達関数は式4です.ポールの周波数は,回路(a)と同じでゼロ点は持ちません.負荷容量により新たに追加されたポールはR1で補償できないのがわかります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

●middlebrook法を用いたループ・ゲインと位相周波数特性のシミュレーション

middlebrook法は Dr. R.David Middlebrookにより1975年に発表された真のループ・ゲインを得る手法です(1).LTspiceにはmiddlebrook法の実用例としてLTspiceインストール・ディレクトリのEducationalフォルダに「LoopGain.asc」というファイル名で格納されています.Windows 7 の環境では,「C:\Program Files\LTC\LTspiceIV\examples\Educational\LoopGain.asc」にあります.

このLoopGain.ascを編集して図1の回路(a)と(b)のループ・ゲインと位相周波数特性をシミュレーションします.

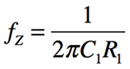

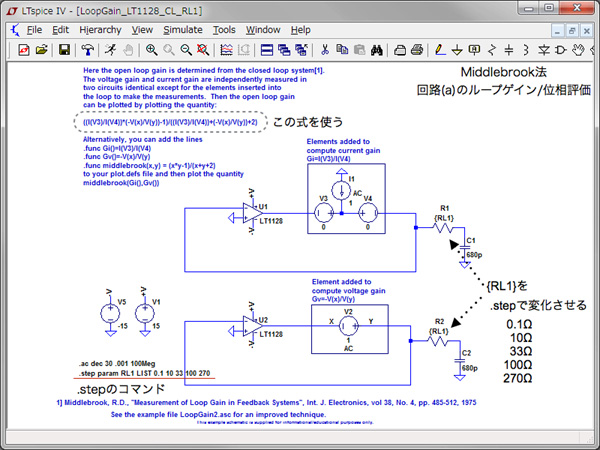

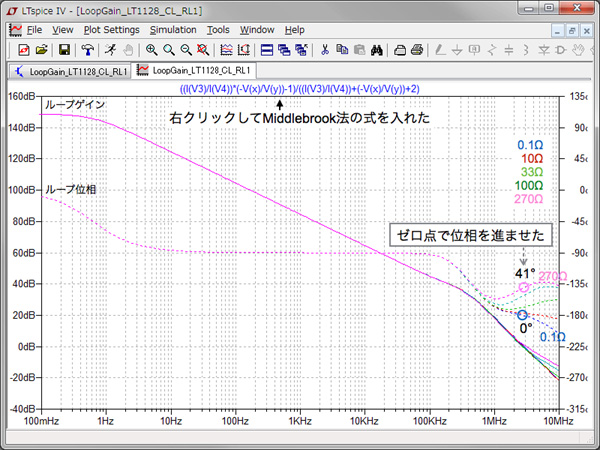

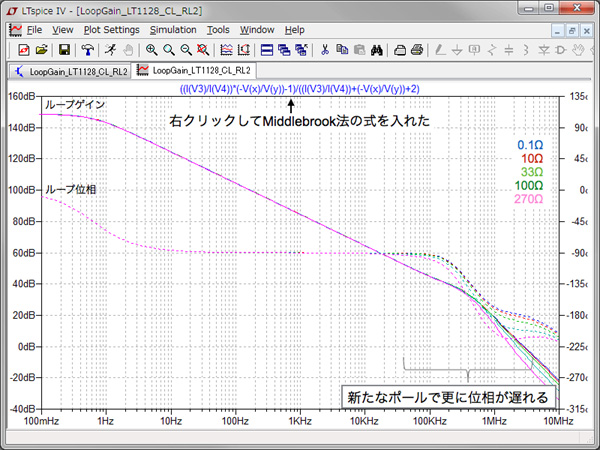

図7は,middlebrook法を用いた回路(a)のシミュレーション回路図です.負荷容量は680pFとし,図1のR1に相当する抵抗は「.step」コマンドで値を 0.1Ω,10Ω,33Ω,100Ω,270Ωと変化させ,ループ・ゲインと位相周波数特性の変化を調べます.

シミュレーション実行後は,任意の回路ノードをクリックしてAC解析の結果を表示させ,その任意の回路ノードを図7中の破線で囲った箇所の式へ置き換えます.複雑な式ですが,コメントとして回路図に入っていますので,コピー&ペーストができます.具体的にはコメントの場所にカーソルをおき,右クリックしてEdit Text on the Schematicのウィンドから該当する数式をテキストとしてコピーします.

図8が図7のシミュレーション結果です.グラフ上部の矢印で示した箇所にカーソルをおき,右クリックして先ほどのmiddlebrook法の式をペーストします.この解析結果より,抵抗を大きくしていくと位相余裕値が増えくるのがわかります.

補償用抵抗の値が大きくなると位相余裕が増える

●過渡解析で発振が抑制されるか確認する

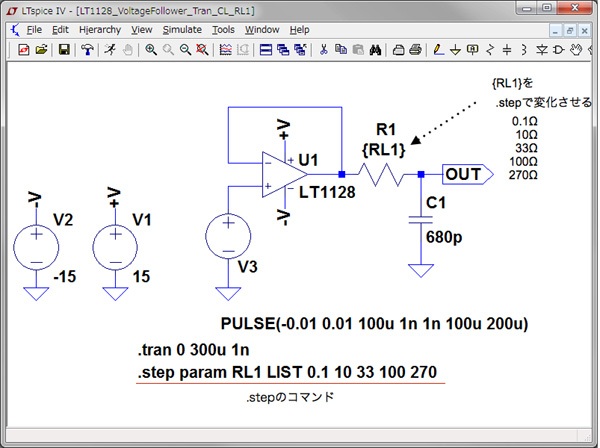

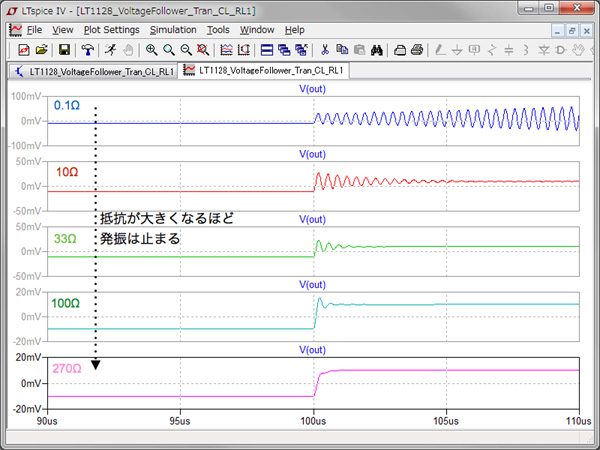

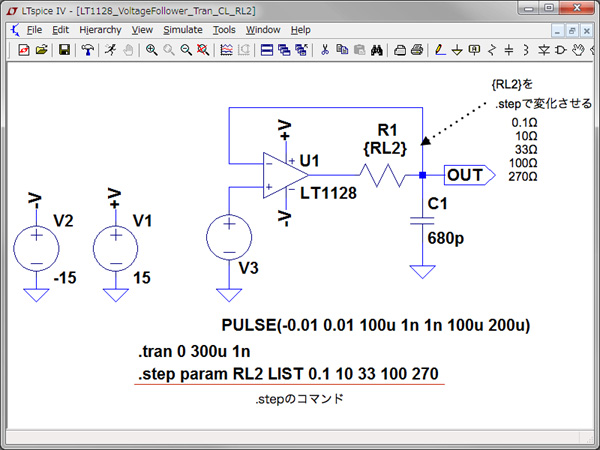

図9は,回路(a)の過渡解析をおこなうシミュレーション回路図です.R1は先程と同様に「.stepコマンド」で値を0.1Ω,10Ω,33Ω,100Ω,270Ωと変化させています.

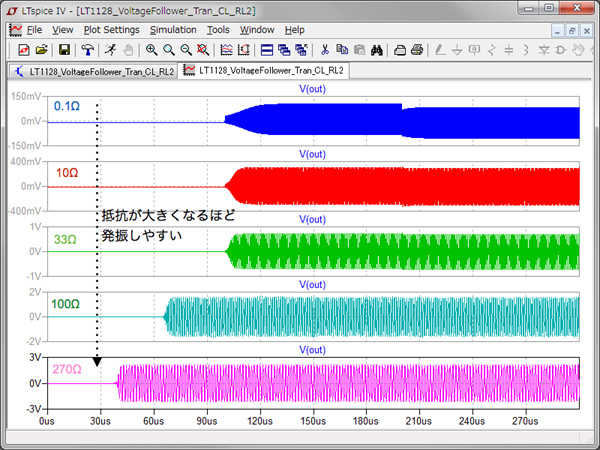

図10は,そのシミュレーション結果で,発振の波形が見やすいように時間軸を拡大し,各抵抗値のシミュレーション結果を並べました.R1の抵抗が大きくなるほど発振は抑えられる様子が分かります.

補償用抵抗が大きくなると発振は停止する

●回路(b)も同様のシミュレーションをしてみる

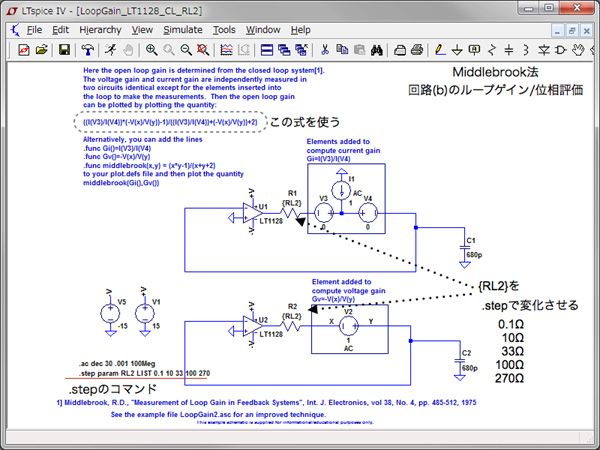

回路(b)においてもmiddlbrook法を用いたループ・ゲインと位相周波数特性をR1の値を「.step」コマンドで値を0.1Ω,10Ω,33Ω,100Ω,270Ωと変化させ,シミュレーションで確かめます.図11がシミュレーションの回路図で,図12がその結果です.

補償用抵抗の値が大きくなると位相余裕が減る

回路(b)は,位相を進ませるゼロ点はなく,R1を大きくするとfpが低くなり,また位相余裕値も少なくなる方向です.負帰還は不安定になり発振しやすくなります.

図13は,過渡解析のシミュレーション回路図で,図14はその結果となります.R1を大きくすると発振振幅が大きくなり,また発振開始の時間も早い時間から起きています.

補償用抵抗が大きくなると発振しやすくなる

●AC解析と過渡解析で回路検証

OPアンプは,オフセット電圧や電流などの直流誤差があります.また,大きな差動ゲインを持つことから負帰還の一部を切断しただけでは,出力が,正か負どちらかの電源電圧へ飽和します.そのため,負帰還による回路の平衡状態を保ちながら,ループを切断するのは至難の技です.このような場合,middlebrook法を用いると,ループを切断することなく計算からループ・ゲインと位相周波数特性が得られ,シミュレーションを使った負帰還の安定性の検証に役立ちます.

周波数特性を見たい時に使うAC解析は,入力端子が電源電圧の中点電位(ここでは±15Vの電源電圧に対し入力はGNDの条件)で小信号AC解析を行い,位相余裕やゲイン余裕を求めています.しかし実際は,信号振幅が大きくなり,また,出力も電源電圧の範囲内で大きな出力電圧となるので,入力がGNDの条件ではありません.小さな振幅では発振しないが,出力波形が電源電圧に近づくと発振するということもあります.負帰還の安定性の検証では,AC解析によるループ・ゲインと位相周波数特性の評価だけでなく,過渡解析を用いて,信号の強弱や回路の周辺温度,素子の許容範囲を考慮して回路検証することが大切です.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice017.zip

●データ・ファイル内容

LoopGain_LT1128_CL_RL1.asc:図7の回路

LT1128_VoltageFollower_Tran_CL_RL1.asc:図9の回路

LoopGain_LT1128_CL_RL2.asc:図11の回路

LT1128_VoltageFollower_Tran_CL_RL2.asc:図13の回路

※ファイルは同じフォルダに保存して,フォルダ名を半角英数にしてください

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs