出力ひずみの少ないサンプル・ホールド回路はどっち?

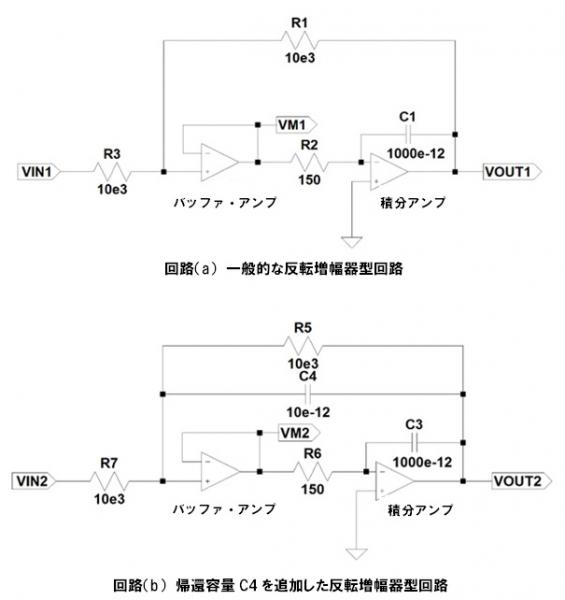

図1の回路(a)と(b)は,反転増幅器型のサンプル・ホールド(S/H)回路です.サンプル・ホールド回路は,ディジタル・オーディオ用などのD-Aコンバータの後段のサンプル開始時にパルス状の入力信号が印加されます.回路(a)と(b)の相違点は,(b)の方に帰還容量「C4」があることです.これらの回路にパルス状の入力信号を印加した場合,出力ひずみの少ない回路はどちらでしょうか?

ただし,スイッチが無いのでこのままでは,サンプル・ホールド回路としては動作しない

回路(b)には,帰還容量「C4」がある

回路(b)

入力から出力への伝達関数は,回路(a)は1次系(1次遅れ要素),回路(b)は2次系(2次遅れ要素)となります.パルス状の入力に対して,2次系の回路は,1次系の回路に比べて出力ひずみを低減しやすい特性を持っています.

●回路の入力から出力への伝達関数を求める

図1の回路(a)と(b)の入力から出力への伝達関数を求めてみます.

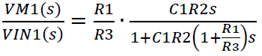

回路(a)の伝達関数は,式(1)のように1次系となります.

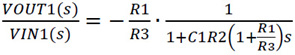

・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・(1)

回路(b)の伝達関数は,式(2)のように2次系となります.

・・・・・・・・・・・・(2)

・・・・・・・・・・・・(2)

式(1)と(2)にそれぞれマイナスがついているのは,反転増幅器構成のためです.

●LTspiceでパルス状の入力に対する応答波形を求める

式(1)と式(2)に,パルス状入力に対する過渡(ステップ)応答は,それぞれの式の右辺に1/Sを乗じて,ラプラス逆変換を行えば,数式的に求められます.ここでは,直観的な理解を得るためにLTspiceを用いて,パルス状の入力に対するステップ応答を確認します.シミュレーションでは,積分アンプとバッファ・アンプは,共に理想OPアンプを用います.

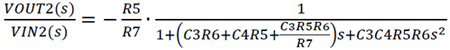

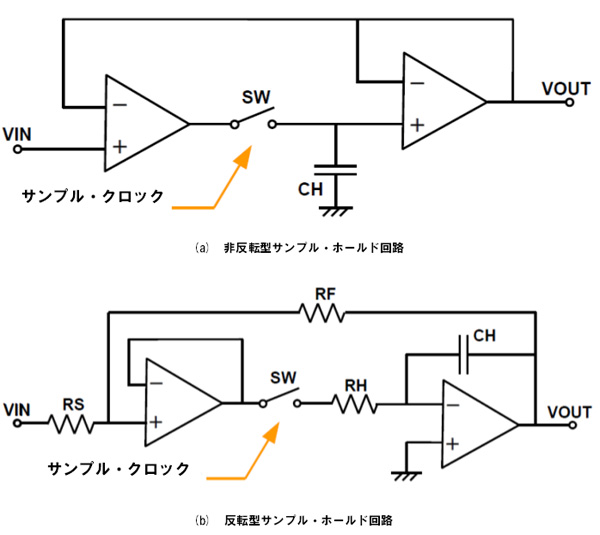

また,図1の回路(a)と(b)は,反転増幅器となっていますので,ステップ応答を行う際,結果がグラフで見やすいように,正負を反転するため,VIN1とVIN2に-1を入力しています.図2にシミュレーション結果を示します.図2(b)は,図2(a)の時間軸を拡大したものです.

図2に示すように,回路(a)の1次系の場合は,時間的に不連続点(t=0で不連続になっている.微分不可能)が生じています.回路(b)の2次系の場合は,S字状に滑らかに立ち上がっている(微分可能)ことがわかります.

不連続点があると実際のアナログ回路では,リンギングや波形の乱れ,遅延が生じます.線形性を保つための必要な回路特性を得るには,回路(b)の方が有利です.回路(b)は,ひずみ発生の原因となるOPアンプ(理想でない実際の)特性への影響が軽減できるため,OPアンプの周波数特性やスルーレートなどの要求仕様を下げることができます.これは,低消費電力化にも繋がります.

このグラフは,結果を見やすいように,正負を反転するため,VIN1とVIN2に-1を入力している

●バッファ・アンプのステップ応答波形を求める

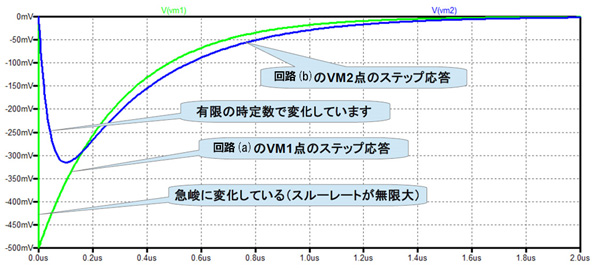

バッファ・アンプのステップ入力に対する応答をLTspiceで確認します.結果を図3に示します.バッファ・アンプの出力VM1,VM2のステップ応答は,回路(a)では急峻に変化している(スルーレートが無限大)のに対して,回路(b)では,有限の時定数で変化しています.ここでも正負を反転するため,VIN1とVIN2に-1を入力しています.

シミュレーションは,理想OPアンプとして実行します.実際の回路では,有限なスルーレートとなるので,この点でも回路(b)が有利です.出力応答波形と同様に回路(a)に比べて,回路(b)の場合は,バッファ・アンプの要求仕様を下げることができます.

このグラフは,結果を見やすいように,正負を反転するため,VIN1とVIN2に-1を入力している

参考までに,図1の回路(a)と(b)の入力からVM1,VM2への伝達関数を式(3),式(4)に示します.

・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・(4)

・・・・・・・・・・・・(4)

以上のように,問題の回路で,帰還容量「C4」を挿入した回路(b)の方が,パルス状の波形入力に対して,ひずみの少ない回路構成になります.

●D-A変換とサンプル・ホールド回路のしくみ

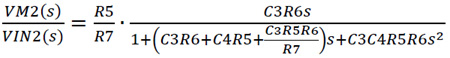

サンプル・ホールド回路は,入力信号をサンプルして一定期間保持(ホールド)する回路です.入力と同極性で出力する「非反転型」と逆極性で出力する「反転型」の二つがあります.一般例を図4に示します.ここでは,反転型の応用例を用いています.

サンプル・ホールド回路は「非反転型」と「反転型」の二つがある

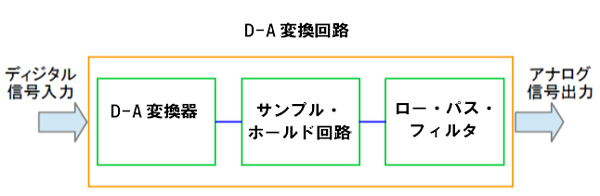

次に,一般的なD-A変換の信号の流れを図5に示します.D-A変換器に入力されたディジタル信号は,D-A変換器によりアナログ信号に変換後,サンプル・ホールド回路に入力され更にロー・パス・フィルタを通して最終のアナログ信号として出力されます.

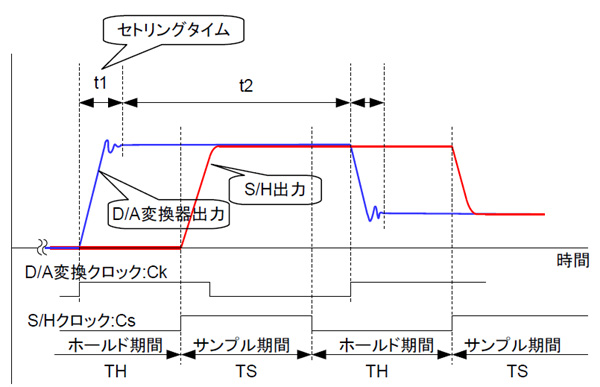

図6にD-A変換器とサンプル・ホールド回路の動作出力波形例を示します.D-A変換器は,変換クロック(Ck)に同期してD-A変換を行います.しかし,変換の間には,最終変換アナログ電圧の1/2LSB内に達するまでの区間(時間t1:セトリングタイム)とD-A変換後のアナログ信号を出力する区間(時間t2)があります.サンプル・ホールド回路は,D-A変換器とは位相の異なったサンプル・ホールド・クロック(Cs)によって動作します.サンプル・ホールド回路では,サンプル時は図4のスイッチ(SW)がオンして,D-A変換後の信号(時間t2内)をサンプル(サンプル・モード期間:TS)します.ホールド時はスイッチをオフにして,次のD-A変換信号をサンプルするまでスイッチ信号をホールド(ホールド期間:TH)します.

D-A変換は,D-A変換クロックCkの立ち上がりで変換を開始.サンプル・ホールド回路は,S/HクロックCsのHレベル時に信号をサンプルし,Lレベルでサンプルした信号を保持(ホールド)する.

この動作は,D-A変換後の信号のみを抽出し,信号品質を劣化させる不要な信号を除去するために行われます.不要な信号とは,D-A変換に要する区間(時間t1)の信号です.

その後,ロー・パス・フィルタ(高域除去フィルタ)により所望のアナログ信号を得ます.ここで,サンプル開始時に着目します.信号を保持するホールド・コンデンサ(図4のCH)には,その前の入力のD-A変換した電圧に相当する電荷が蓄積(ホールド)されています.サンプル開始時には,図4でスイッチがオンし,前回のD-A変換値と次のD-A変換値の差分にあたるパルス状の信号が入力されることになります.

例えば,前回のD-A変換値が,ゼロ(ホールド・コンデンサには蓄積された電荷はゼロ)で,次のD-A変換値が1の場合は,サンプル開始時にサンプル・ホールド回路には,振幅1のステップ入力が印加されることになります.

●サンプル・ホールド回路の動作を確認する

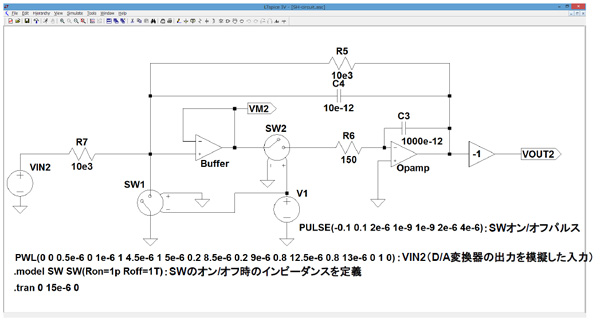

図7は,回路(b)にサンプル・ホールド動作を行わせるためのスイッチ(SW1,SW2)を追加した回路です.これらのスイッチは,逆相でスイッチさせます.サンプル時,SW1はオフ,SW2はオンとなりD-A変換器出力信号をサンプル・ホールド回路に伝えホールド・コンデンサに信号を蓄積します.一方,ホールド時は,SW1はオン,SW2はオフで,D-A変換器の出力を遮断し,サンプルした信号を保持します.

図4(b)の回路にSW1を加える理由は,D-A変換器の変換動作時の出力の漏れを最小にするためです.実際の回路の場合,サンプル・ホールド回路の出力のOPアンプは有限のインピーダンスを持つからです.前述のように,図1の回路は,反転型サンプル・ホールド回路です.そこで,図7では結果がグラフで見やすいようにサンプル・ホールド回路出力に極性の正負を反転する-1倍のバッファを追加してあります.また,D-A変換器出力信号はダミーとして,PWL信号源で定義しました.SW1とSW2のオン・オフの制御信号は,信号源V1(PULSE)で与え,SW1とSW2のオン・オフ時のインピーダンス(抵抗値)は,「.MODEL」でそれぞれ記述しました.

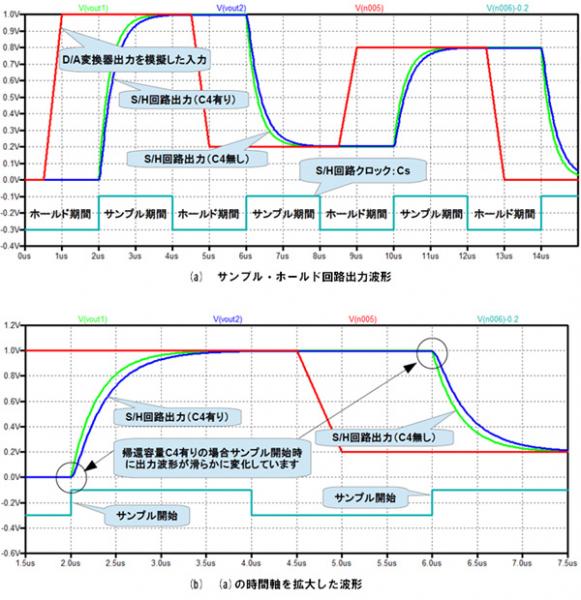

図8にシミュレーション結果を示します.図8(b)は,(a)のシミュレーション結果の時間軸を拡大したものです.比較のため,帰還容量「C4(10pF)」がある場合と無い場合の両方を示しました.C4がある場合は,図2と同じようにサンプル開始時に出力は滑らかに変化していることが確認できます.見やすいように,サンプル・ホールド・クロックは,マイナス側にシフトして描いています.

C4がある場合サンプル開始時に出力は滑らかに変化する

●終わりに

今回は,回路(b)のように,帰還容量「C4」を追加するだけで,回路の伝達関数の次数を変えて,ひずみ特性の劣化を抑え,積分アンプやバッファ・アンプなどの要求仕様を下げることを定性的に示しました.実際の回路設計では,ここで紹介した方法とは別の構成で,同様なことが実現できる可能性があります.他のさまざまな回路でも設計仕様を保ちつつ,このような手法(伝達関数を少し変える)を応用してはいかがでしょうか.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice012.zip

●データ・ファイル内容

Circuit(a)(b).asc:図1の回路(a)と(b)の回路

Opeamp.asc:積分アンプ用の理想OPアンプの回路

Opeamp.asy:積分アンプ用の理想OPアンプのシンボル

Buffer.asc:バッファアンプ用の理想OPアンプの回路

Buffer.asy:バッファアンプ用の理想OPアンプのシンボル

Buffer-1.asc:正負を反転する-1倍のバッファ回路

Buffer-1.asy:正負を反転する-1倍のバッファ回路のシンボル

SH-circuit1.asc:図7の回路

SH-circuit1.plt:グラフ表示用のファイル

※ファイルは同じフォルダに保存して,フォルダ名を半角英数にしてください

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら