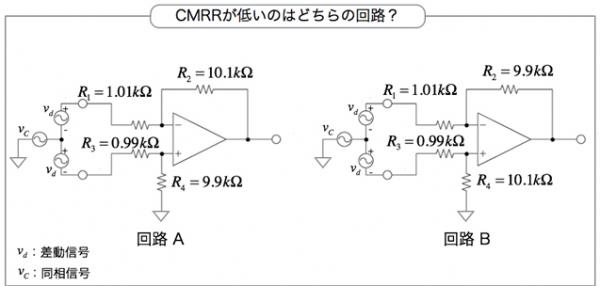

CMRRが低いのはどちらの回路?

理想的な差動増幅器は,同相信号を入力しても出力は0です.実際は同相入力を与えたことにより僅かながら出力に変化が表れます.それでは,図1の1%の抵抗誤差を与えた回路Aと回路Bで,同相の信号を除去する能力(CMRR :Common Mode Rejection Ratio:同相信号除去比)が低いのはどちらの回路?

ここではOPアンプと抵抗を用いた差動増幅器において抵抗の誤差により生ずるCMRRについて考えます.

R1とR3は1kΩ,R2とR4は10kΩとし1%の誤差を持つ抵抗で二つの差動増幅器を作ったところ回路A, 回路Bの各抵抗値は,抵抗の誤差により図1のようになりました.「R1=R3,R2=R4でR2/R1=R4/R3」であればOPアンプの持つ高いCMRRが得られますが,実際は抵抗の誤差によりCMRRが低くなります.二つの回路において抵抗の誤差によるミスマッチの効果でCMRRが低いのはどちらの回路でしょうか?

ただし,OPアンプの誤差を無視するため,二つのOPアンプは直流誤差が無く,オープンループ利得は無限大,同相利得はゼロの理想OPアンプとし,回路A,回路BのOPアンプは同特性とします.

回路B

R2/R1とR4/R3の二つの比の差が増すほどCMRRは低くなる.

●CMRRとはなんでしょうか

同相信号の多くは,差動信号の二つの信号に同時に載った同相のノイズ成分と見なされ,コモン・モード・ノイズと言われています.

CMRRとは,OPアンプで構成した増幅器のコモン・モード・ノイズを除去する能力です.

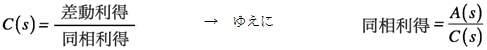

同相信号除去比は「差動利得/同相利得」の比で求められ,この比が大きいほど差動増幅器として性能が高くなります.差動増幅器の望ましい差動利得と望ましくない同相利得の比を使った増幅回路の特性を表す指標の一つです.

差動利得をA(s),CMRRをC(s)で表すと差動利得,同相利得,CMRRは次の関係です.

●電子部品には誤差があります

OPアンプを用いた差動増幅器を設計するときR1=R3,R2=R4とし,R2/R1=R4/R3の比が必要な利得となるようにします.しかし抵抗には誤差があり,「E96系列で1kΩをください」と注文しても実際は1kΩ±1%の抵抗が届きます.

部品には誤差があり回路設計で設定した「R1=R3,R2=R4でR2/R1=R4/R3」とはなりません.この場合,回路設計者は部品に誤差があっても最小値と最大値の規格を満足するよう設計を進めます.回路設計者は部品が持つ誤差の組み合わせで特性がどう変わるのか知っておくことが大変重要です.

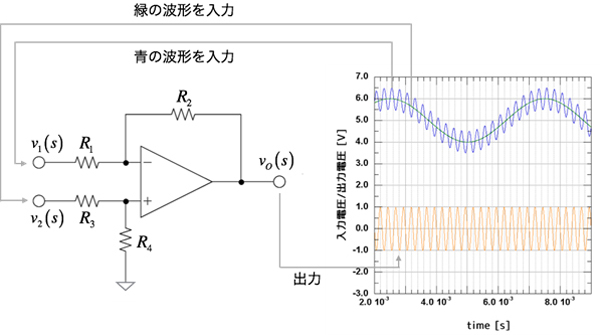

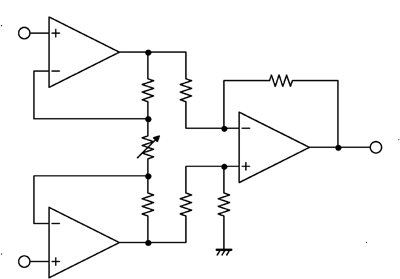

●差動増幅回路は,同相の信号を除去します

OPアンプを使った応用例で,図2に示す差動増幅回路があります.差動増幅回路は入力の差信号を増幅し同相入力の多くをノイズとして除去する便利な回路です.差動増幅回路を使った応用例として二つの入力の前段に更にOPアンプを追加した図3の計装増幅器(Instrumentation Amplifier)は有名で大きな同相入力環境下で利用されます.また,雑音(ノイズ)が大きな環境下で使用するなど産業用途で使われています.差動増幅回路出力の誤差はOPアンプの誤差や抵抗の誤差により発生します.ここでは,OPアンプは誤差要因を含まない理想OPアンプを使用し抵抗の誤差による影響,特にCMRRについて考えてみたいと思います.

なお,OPアンプのCMRRは多くの場合直流での値が示されその周波数特性は直流で最大値となる特性です.LM101のカタログにはCMRRの周波数特性が記載されていますがこれは稀な部類です.

差動増幅回路は入力の差信号を増幅し同相入力の多くをノイズとして除去します

同相信号が除去され差動信号を増幅した波形が表れます

二つの入力の前段に更にOPアンプを追加した計装増幅器.ノイズが大きな環境下で使用するなど産業用途で使われています

●LTspiceで抵抗の誤差が回路へ及ぼす影響を調べてみよう

LTspiceを使い差動増幅回路の二つの入力端子へ同相入力電圧を印加し出力電圧がどのように動くかを抵抗の誤差がない回路とある回路で比較してみましょう.同相入力で出力が変化するようであれば同相利得があることになりCMRRの定義式より影響を及ぼすか否かすぐ分かります.図1の信号源は交流ですが,数値例では非常に低周波のCMRR,いいかえれば直流でのCMRRの変化を比較します.

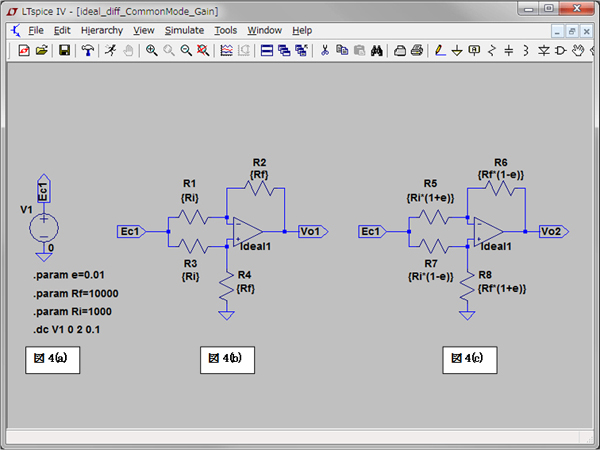

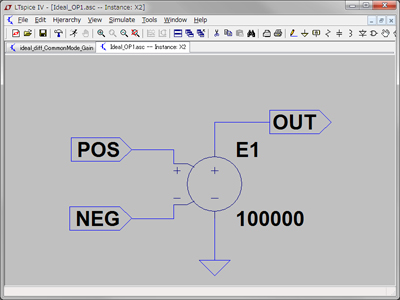

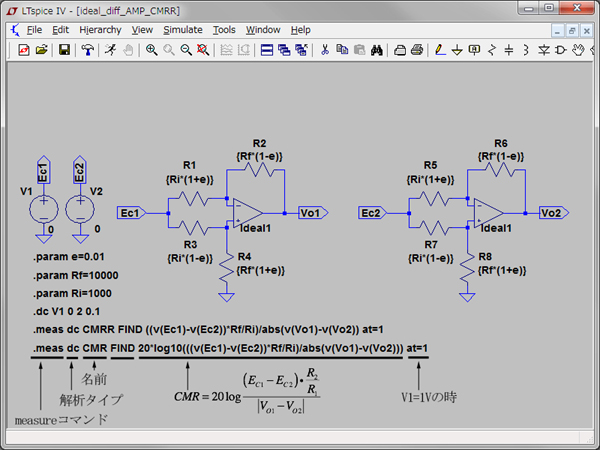

図4が実験用のLTspiceの回路です.OPアンプは図5に示す電圧制御電圧源で無限大周波数まで利得が10000倍(100dB)とした理想OPアンプでこれを三角形のOPアンプシンボルへ関連づけています.OPアンプのカタログに出てくる直流誤差,例えばオフセット電圧等はありません.電圧制御電圧源は二つの入力端子間の電圧を与えた倍率で出力する理想素子でSPICEのエンジンによって呼び名が少しかわります.LTspiceではVoltage depended voltage sourceとしてコンポーネントの中にあります.図4の回路図からOPアンプシンボルの三角形の上にマウスカーソルを置き,右クリックして開いた「Navigate/Edit Schematic Blockウィンド」の「Open Schematic」を押すと図5の回路が確認できます.

図4(a) 図1の回路A,回路Bへ印加する電圧源V1とLTspiceのコマンド類

図4(b) 図1の回路AをLTspiceで記述した回路

図4(c) 図1の回路BをLTspiceで記述した回路

●抵抗の誤差はCMRRが変化します

図4の実験用回路は.paramを用い変数に値を代入しその変数を抵抗値としています.抵抗値の波括弧({ }の記号)で囲われたもの({Ri}など)がそれで,LTspiceでは波括弧を使うことにより変数を扱えるようになります.

左側の回路はR1=R3, R2=R4 となり抵抗の誤差はありません.一方,右側の回路は.param e=0.01で与えた誤差:1%で差動増幅器の誤差が最大になるように与えています.左右二つの回路の同相入力電圧は電圧源V1で0~2Vを0.1Vステップで印加しています.

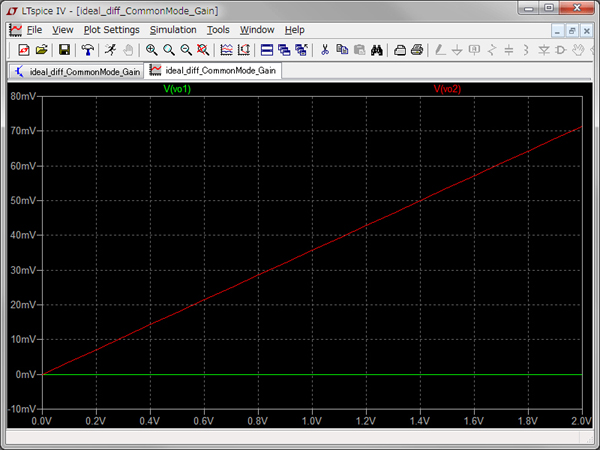

シミュレーションで得られた結果を図6に示します.横軸がV1の印加電圧,縦軸が出力電圧です.緑色は抵抗誤差がない右側の回路,赤色は1%の抵抗誤差があるものです.

抵抗誤差がない理想状態の左側の回路では同相入力電圧を印加しても出力電圧は動きませんが抵抗誤差がある右側の回路は同相入力電圧により出力電圧が変化しています.これからも明らかなように抵抗の誤差による有限の同相利得がありCMRRの定義式中の分母が変化しますからCMRRが低くなるのは確実です.

●抵抗誤差が1%でシミュレーションします

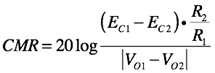

では,抵抗誤差でCMRRがいくらになるか図7の回路を用いてシミュレーションしてみましょう.この測定方法は電子情報技術産業協会規格:EIAJ ED-5103A 「リニア集積回路測定方法(演算増幅器及びコンパレータ)」のCMRRを測定する方法です.被測定回路へ異なる直流電圧を印加し,得られた二つの出力電圧からCMRRを計算する方法で次の式(1)から求められます.

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

CMR(Common Mode Rejection)はCMRRの20logをとります.単位は[dB]として表した値で使われています.本来この方法はOPアンプのCMRを測定する方法ですがここではOPアンプは理想状態で抵抗誤差がある場合の測定として使います.EIAJ ED-5103Aは電子情報技術産業協会のホームページから閲覧が可能です.

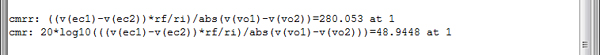

図7では1回のシミュレーションでCMRが計算できるよう左右に同じ回路を登録して異なる印加電圧を同時に与えています.この二つの回路を用い.measコマンドでCMRRとCMRが計算できるようにしました.シミュレーション終了後に.measコマンドで計算した値はログファイル中にあり,メニューバーの,「View > SPICE Error Log」または,ショートカットの「Ctrl + L」でログファイルのウィンドが開きますのでそこで値が読めます.

図8がログファイルの一部で CMRR=280.053倍,CMR=48.9448dBが読み取れます.このように抵抗誤差が1%で差動増幅器のCMRは48.9dBしかないことが分かります.

●計算式による検証

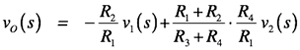

図2に示す理想OPアンプを用いた差動増幅器の出力は重ね合わせの理を用いて計算すると,

・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・(2)

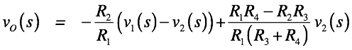

これを二つの入力端子間の差信号を増幅する形へ変形します.

・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・(3)

式(3)の右辺第一項はR1とR2の抵抗比で決まる差動利得で入力の差信号を増幅しています.これが差動増幅器として使いたい回路の差動利得であり設計者が優先するものです.また,右辺第二項は抵抗のミスマッチによる出力電圧の誤差を示しています.設計者は差動増幅器として回路定数を決めるときR1=R3, R2=R4とします.R1R4=R2R3 すなわちR2/R1=R4/R3なら誤差を含まない完全な差動増幅回路になりますが完全にR1=R3,R2=R4にするが難しく,抵抗比のミスマッチによって差動増幅利得以外に誤差を含んだものが出力に現れるのが理解できるでしょう.

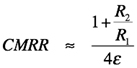

差動増幅回路の抵抗ミスマッチによるCMRRは式(4)で求めることができεは抵抗の誤差を表しています.これからも明らかなようにCMRRを大きな値にするには分子にある回路の差動利得を大きくするか分母にある抵抗の誤差を小さくするしか方法がありません.先ほどのシミュレーションで与えた回路定数と同様のε=0.01とし抵抗の誤差1%で計算すると R1=1kΩ,R2=10kΩの条件で CMRR=275倍 CMR=48.79dBとなりシミュレーション結果とほぼ一致します.苦労をして差動増幅器の4本の抵抗を選別し0.1%にしたとしても式3よりCMRは68.79dBにしかなりません.図7のLTspiceの回路図でe=0.01へマウスカーソルをあて右クリックで値が編集できますので e=0.001と変更してシミュレーションを実行し確認してみて下さい.このような実験を繰り返して得た結果や電気的特性に記載されているOPアンプの他の誤差要因も考慮するとOPアンプ1つと4本の抵抗で作る差動増幅回路の限界が見えてくると思います.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice001.zip

●データ・ファイル内容

ideal_diff_CommonMode_Gain.asc:図4の回路

ideal_diff_AMP_CMRR.asc:図7の回路

Ideal_OP1.asc:図5(理想OPアンプの回路)

Ideal_OP1.asy:OPアンプのシンボル

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら