降圧スイッチング電源のゲインと周波数の特性

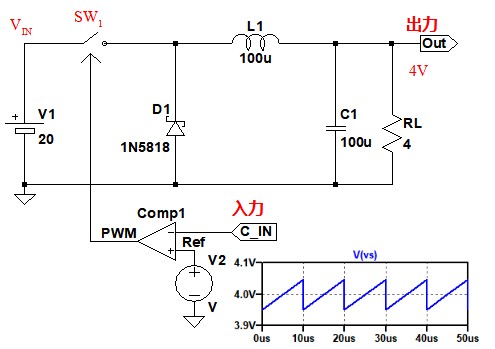

図1は,PWMコンパレータの出力でSW1のオン・デューティ比を制御する,出力電圧4Vの降圧スイッチング電源のブロック図です.コンパレータ(Comp1)の+入力(Ref)には基準信号として,平均電圧4Vで振幅0.1Vののこぎり波が加えられています.この回路に,出力電圧を一定にするための帰還回路を追加します.

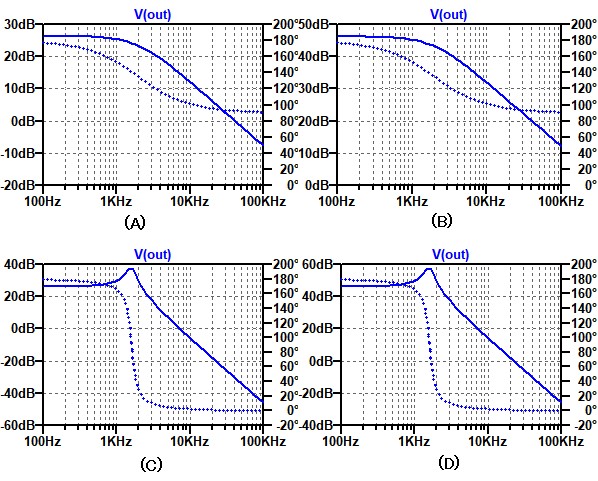

帰還回路を設計する準備として,図1の回路を小信号等価回路に置き換え,ゲインと位相のシミュレーションを行いました.Comp1の-側入力(C_IN)から信号を加えたときの,出力端子(Out)のゲインと位相の特性として,正しいのは図2の(A)~(D)のどれでしょうか.

ただし,等価回路に置き換える条件は,入力電圧20V,出力電圧は約4Vで,電流連続モードで動作しているものとする.また,図2の実線がゲインで破線が位相を表している.

図1の回路を小信号等価回路に置き換えるには,まず,直流ゲインを求める必要があります.降圧スイッチング電源の出力電圧は,入力電圧にスイッチのオン・デューティ比を掛けたものです.コンパレータの入力電圧変化に対する,出力のデューティ比の変化の割合を計算し,それに入力電圧を掛け合わせれば,出力電圧の変化の割合,つまりゲインが計算できます.直流ゲインが分かれば,あとはそこに,コイルやコンデンサ,抵抗から構成されたフィルタの周波数特性を重ね合わせれば,答えが分かります.

図1は,基準信号の振幅が0.1Vなので,Comp1の-側入力が0.1V変化するとオン・デューティ比が0~100%まで変化します.入力電圧が20Vなので,結局0.1Vの入力変化で20V出力電圧が変化することになり,ゲインは46dBと計算できます.また,コイルやコンデンサ,抵抗から構成されたフィルタは,2次特性となりゲインが40dB/decで減衰します.直流ゲインが46dBで,40dB/decで減衰しているグラフは(D)です.なので正解は,(D)となります.

●小信号等価回路のゲインと周波数の特性

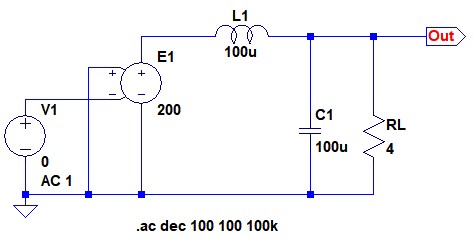

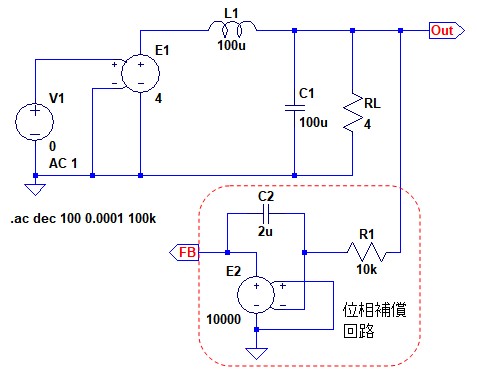

図3は,図1の小信号等価回路です.電圧制御電圧源(E1)が,コンパレータ入力端子から出力までの直流ゲインを表しています.

PWMコンパレータはゲイン200倍の電圧制御電圧源に置き換える.

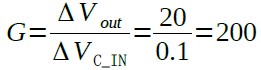

図1の回路でコンパレータの+入力(Ref)には,基準信号として平均電圧4Vで振幅0.1Vののこぎり波が加えられています.コンパレータの-入力(C_IN)が3.95V以下になるとPWM出力のオン・デューティ比は100%となり,4.05V以上でオン・デューティ比は0%になります.つまり,0.1Vの電圧変化でオン・デューティ比は100%変化することになます.出力電圧は入力電圧にオン・デューティ比を掛け合わせたものです.入力電圧は,20VなのでC_INが0.1V変化すると出力が20V変化することになります.そのため,直流ゲイン(G)は式1のように200倍(46dB)となります.

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

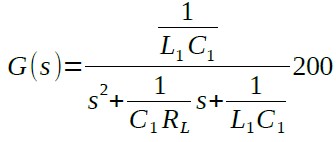

式1の結果からE1のゲイン係数は200倍となっています.また,L1,C1,RLでフィルタを構成しており,図3の伝達関数は式2のように表されます.

・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・(2)

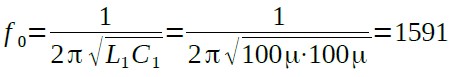

式2から分かるように,図3は,2次のローパス特性を示します.また,カットオフ周波数(f0)は式3で計算することができます.

・・・・・・・・・・・・(3)

・・・・・・・・・・・・(3)

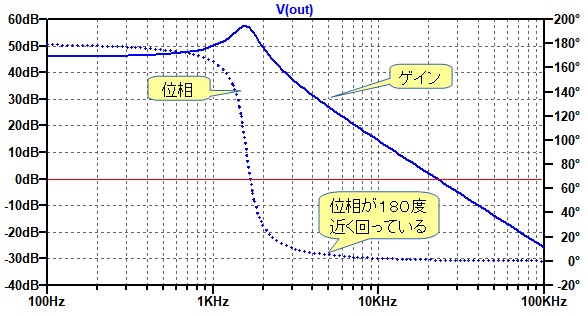

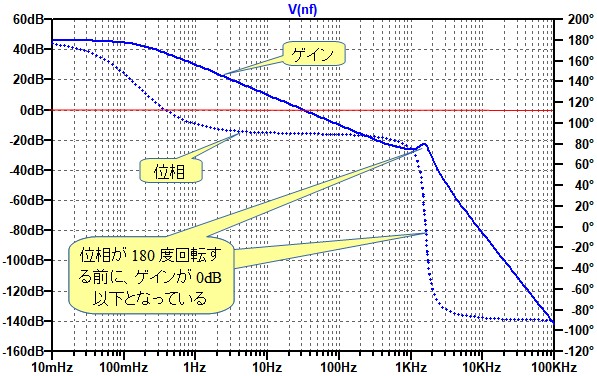

図4は,図3のシミュレーション結果です.ゲインは,1.6kHz付近にピークのあるローパスフィルタ特性となっています.これは,図2の(D)と同じものです.図4を見ると,カットオフ周波数付近で急激に位相が変化し,ゲインが0dBになる前に位相が180度近く回転していることが分かります.負帰還回路では,ゲインが0dB以上ある状態で,位相が180度回転すると,正帰還になってしまい,システムが発振してしまいます.そのため,図1の回路で出力電圧を一定にするための帰還回路を構成する場合,位相補償回路が必要になります.

ゲインが0dBになる前に位相が180度近く回転している.

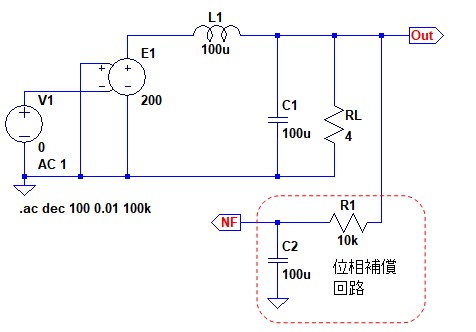

●抵抗とコンデンサによる位相補償回路

最も簡単な位相補償回路は抵抗とコンデンサによるローパスフィルタです.カットオフ周波数を十分に低く設定し,位相が180度回転する前にゲインを0dB以下とすることで,システムが発振しないようにできます.図5は,図3の回路に抵抗(R1)とコンデンサ(C2)からなる位相補償回路を追加したものです.

抵抗とコンデンサでローパスフィルタを構成し,ゲインを下げる.

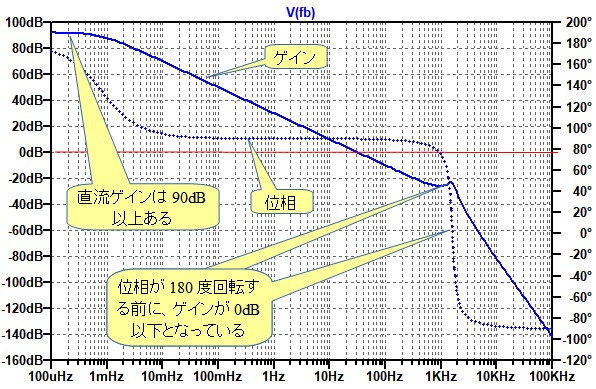

図6は,図5のシミュレーション結果です.位相補償回路として追加したローパスフィルタのカットオフ周波数は0.16Hzです.ゲインはカットオフ周波数以降,20dB/decで減衰していくため,位相が180度回転する前に,0dB以下になっています.位相が180度回転したときのゲインは-22dBでゲイン余裕は20dB以上あり,この特性であればシステムが発振することはありません.この位相補償回路は,「LTspice 電源&アナログ回路入門 038 ―― スイッチング電源のPWMコンパレータの動作」で使用したものです.

位相が180度回転する前に,ゲインが0dB以下となっている.

●積分回路による位相補償回路

図5の回路は,直流ゲインが46dBとあまり大きくないため,「スイッチング電源のPWMコンパレータの動作」で説明したように,入力電圧の変動により,出力電圧が多少変動してしまいます.図5と同様な位相補償を行いながら,さらに,直流ゲインを大きくするために,積分回路を使用する方法があります.

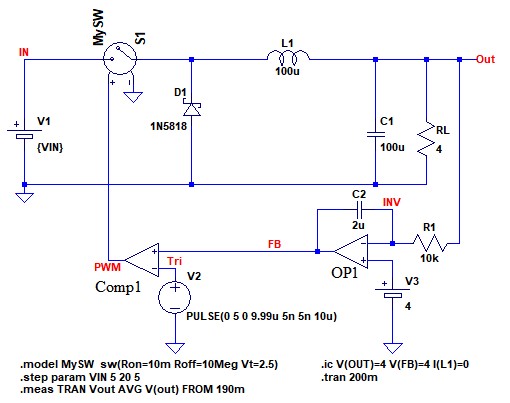

図7は,図5の位相補償回路を積分回路に変えたものです.ゲイン10000倍(80dB)の電圧制御電圧源(E2)をオペアンプとして使用しC2で帰還をかけた反転増幅型積分回路になっています.PWMコンパレータのゲインは,振幅5Vの基準信号を使用することを想定し,4倍としてあります.

C2で帰還をかけた反転増幅型積分回路となっている.

図8は,図7のシミュレーション回路です.直流ゲインは90dB以上あり,図6と比べてかなり大きくなっていることが分かります.直流ゲインは,大きくなっていますが,カットオフ周波数も下がっているため,図6と同様,ゲインは位相が180度回転する前に0dB以下となっています.

直流ゲインは90dB以上と大きいが,ゲイン余裕は20dB以上ある.

●積分回路による位相補償を使用した降圧スイッチング電源

図9は,積分回路による位相補償を使用した回路です.PWMコンパレータの基準信号は振幅5Vののこぎり波となっています.積分回路が反転増幅タイプのため,積分回路出力はPWMコンパレータの+入力端子に接続して,負帰還がかかるようになっています.また,積分回路を構成しているオペアンプ(OP1)の+入力端子に直流基準電圧の4Vが接続されています.出力電圧はこの直流基準電圧と等しくなるよう,フィードバックがかかります.この回路で入力信号を5Vから20Vまで5Vステップで変化させてシミュレーションを行います.

積分回路出力はPWMコンパレータの+入力端子に接続.

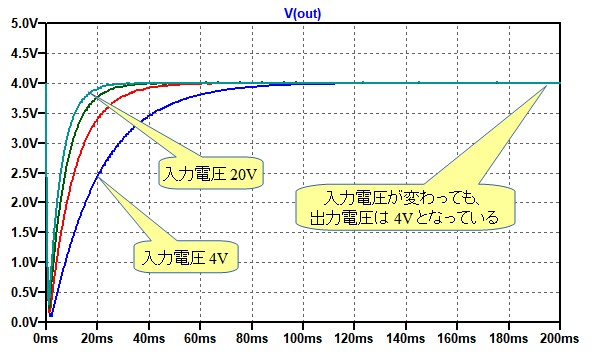

図10は,図9のシミュレーション結果です.入力電圧が変化しても最終的な出力電圧は4Vとなっていることが分かります.

入力電圧が変化しても最終的な出力電圧は4Vとなっている.

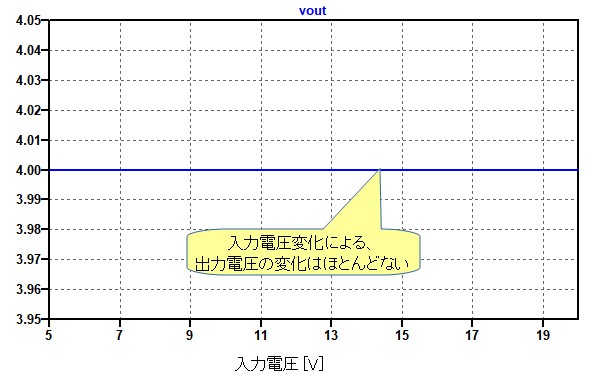

図11は「.mearsコマンド」を利用して,各シミュレーション最後の10msecの平均電圧を計算し,入力電圧を横軸にしてプロットしたものです.入力電圧が変化しても出力電圧がほとんど変化していないことが分かります.

入力電圧が変化しても出力電圧はほとんど変化していない.

以上,降圧スイッチング電源のゲインと位相の周波数特性と,位相補償の方法を解説しました.図5や図7のような位相補償回路は,システムとして発振しないようにするため,カットオフ周波数を低く設定し,高域のゲインが小さくなるようにします.すると入力電圧や負荷が急変したとき,フィードバックの応答が遅れ,出力電圧の変動が大きくなってしまいます.位相補償の考え方を分かりやすく説明するため,図5や図7の回路を使用しましたが,実際の製品では,もう少し工夫された位相補償回路が使われています.その位相補償回路に関しては改めて解説する予定です.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice3_040.zip

●データ・ファイル内容

LC_LPF_D.asc:図3の回路

LC_LPF_RCNF.asc:図5の回路

LC_LPF_INTNF.asc:図7の回路

Step_down_PWM_INT.asc:図9の回路

LimitAmp.asy:図9の回路で使用しているコンパレータのシンボル

LimitAMP.asc:図9の回路で使用しているコンパレータの内部回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs