ゲインが20dBとなる差動増幅回路のテール電流値は?

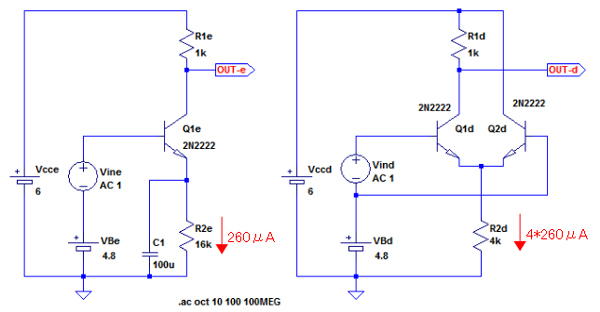

図1(左)は,電流帰還バイアス回路を使用したエミッタ接地増幅回路です.図1(右)は,二つのトランジスタ(Q1,Q2)で構成した差動増幅回路です.どちらの回路も,電源電圧(VCC)が6Vで,電圧源(VB)でベース・バイアス電圧を4.8V与え,負荷抵抗(R1)が1kΩとなっており,OUT端子までのゲインは20dB(10倍)となっています.

この条件で,図1(左)のエミッタ接地増幅回路のエミッタ抵抗(R2)には,260μAの電流が流れています.この場合,図1(右)の差動増幅回路のエミッタ抵抗(R2)に流れる必要な電流値は,次の(A)~(D)のどれになるでしょうか?

差動増幅回路(右)のR2の電流はいくつにすればよいのか.

図1(右)の差動増幅回路でQ1とQ2のベース直流電圧は等しくなっています.そのため,Q1とQ2のエミッタ電流は等しく,Q1とQ2のエミッタ電流の合計値は,R2に流れる電流と等しくなります.また,ゲインと負荷抵抗(R1)の値から差動増幅回路に必要なgm(相互コンダクタンス)が分かります.gmの値がわかれば各トランジスタに流すべき電流値を求めることができます.

図1(左)のエミッタ接地増幅回路と図1(右)の差動増幅回路の負荷抵抗(R1)の値は1kΩで,また,ゲインも20dBで同じです.なので,差動増幅回路のgmは,エミッタ接地増幅回路のgmと同じになります.差動増幅回路では,トランジスタQ1とQ2の電流はそれぞれ,エミッタ抵抗(R2)に流れている電流の1/2になります.また,入力信号に対してQ1とQ2が直列に接続されているため,差動増幅回路のgmはトランジスタ(Q1,Q2)単体のgmの1/2になります.そのため,差動増幅回路のgmはエミッタ接地増幅回路のgmと比べると1/4になります.

そこで,差動増幅回路のgmをエミッタ接地増幅回路のgmと同じにするためには,差動増幅回路のR2に流れる電流をエミッタ接地増幅回路のR2に流れる電流の4倍にする必要があります.エミッタ接地増幅回路の電流は260μAなので,差動増幅回路のR2に流れる電流は,260μAを4倍し1040μA必要となります.なので,正解は(D)ということになります.また,差動増幅回路のR2の抵抗値は,エミッタ接地増幅回路のR2の1/4なので4kΩになります.

●差動増幅回路のgmの求め方

図1(右)の差動増幅回路の抵抗(R2)に流れる電流のことをテール電流(tail current)と呼びます.テール電流と差動増幅回路のgmの関係式を求める方法はいろいろあります.ここでは,エミッタ接地増幅回路と対比する形で差動増幅回路のgmを求める方法と差動増幅回路の入出力特性からgmを求める方法を解説します.

●エミッタ接地増幅回路との対比で差動増幅回路のgmを求める

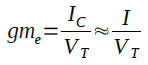

図1(左)のエミッタ接地増幅回路において,エミッタ抵抗(R2)に流れる電流をIとします.ベース電流を無視するとQ1のコレクタ電流(IC)は,Iと等しくエミッタ接地増幅回路のgm(gme)は式1で表すことができます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(1)

K:ボルツマン定数,T:絶対温度,q:電子電荷

K:ボルツマン定数,T:絶対温度,q:電子電荷

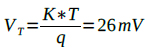

図1(右)の差動増幅回路のR2に流れる電流をITとします.ベース電流を無視するとトランジスタQ1とQ2のコレクタ電流は,それぞれIT/2になります.ここでQ1とQ2の等価抵抗をre1とre2とします.re1とre2は式2で表されます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

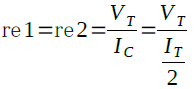

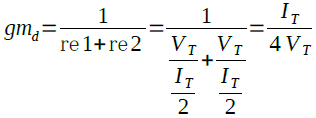

図1(右)の差動増幅回路では,入力信号に対してQ1とQ2が直列になっているとみなせるため,差動増幅回路のgm(gmd)はre1とre2を合計した値の逆数になり,式3で表すことができます.

・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・(3)

式1と式2を比較すると,R2の電流が同じ場合,差動増幅回路のgmはエミッタ接地増幅回路のgmの1/4になることが分かります.逆に言えば,同じgmとするためには4倍の電流を流す必要があります.

●差動増幅回路の入出力特性からgmを求める

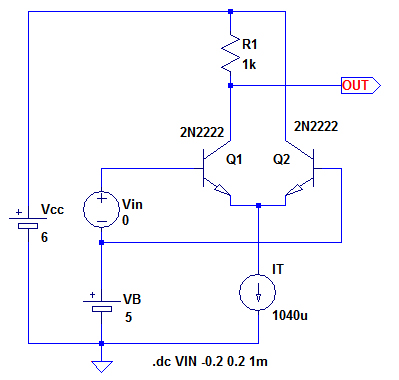

図2は,差動増幅回路の入出力特性を確認するための回路です.図1(右)でエミッタに接続されていた抵抗(R2)は,シミュレーションを正確にするため,定電流源に置き換えています.

エミッタ抵抗は定電流源ITに置き換えている

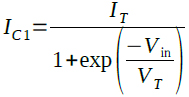

図2の回路において,入力信号(Vin)に対するQ1のコレクタ電流(IC1)およびQ2のコレクタ電流(IC2)はベース電流を無視すると式4,式5で表されます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

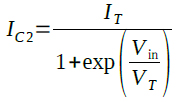

図3は,図2の回路で入力信号(Vin)に対するQ1のコレクタ電流(IC1)およびQ2のコレクタ電流(IC2)をシミュレーションしたものです.Vinが0Vのときは,それぞれITの1/2の電流が流れ,Vinがおよそ±100mV以上になると,どちらか一方だけに電流が流れるようになります.

入力電圧が0Vの時はそれぞれITの1/2の電流が流れる

図3のコレクタ電流のグラフの傾きがgmです.そのため,式4をVinで微分することで,式6のようにgmを求めることができます.

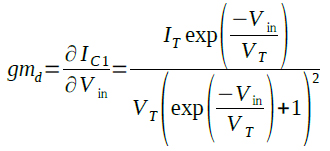

・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・(6)

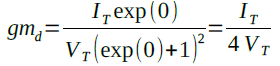

式6はVinとgmの関係を表した式ですが,Vinに0を代入することで,式7のように入力直流電圧が0Vのときのgmが得られます.

・・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・・(7)

式7のようにして計算した差動増幅回路のgmは,式3と同じになります.

図4は,図3のQ1のコレクタ電流(Ic(Q1))を横軸のVinで微分したものをグラフ化したものです.入力電圧によるgmの変化を表しています.入力電圧が大きくなると急激にgmの値が小さくなっていることが分かります.そのため一般的には差動増幅回路にはあまり大きな信号を加えることができません.ただし,図3のような特性を利用し,入力信号を故意にクリップさせるリミッタ回路として差動増幅回路を使用する場合もあります.OPアンプの入力段に差動増幅回路を使用した場合は,負帰還の効果により+入力と-入力に加わる電圧は非常に小さくなるため,この特性は問題になりません.

入力電圧が大きくなると急激にgmが低下する

●エミッタ接地増幅回路と差動増幅回路のゲインをLTspiceで確認する

図5は,図1の(左)と(右)をシミレーションする回路です.素子番号の重複を避けるため,末尾にeとdを加えています.

差動増幅回路のテール電流はエミッタ接地増幅回路の4倍としている.

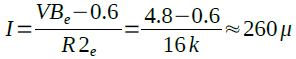

エミッタ接地増幅回路の電流(I)はトランジスタのベース・エミッタ間電圧を0.6Vとすると,式8で計算できます.

・・・・・・・・・・・・・・・・・・・・・・(8)

・・・・・・・・・・・・・・・・・・・・・・(8)

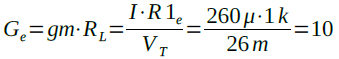

また,そのゲイン(Ge)は式9で計算することができ,20dB(10倍)となります.

・・・・・・・・・・・・・・・・・・・(9)

・・・・・・・・・・・・・・・・・・・(9)

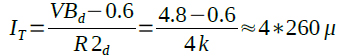

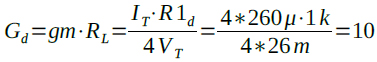

差動増幅回路のテール電流をエミッタ増幅回路の4倍とするため,R2dは,R2eの1/4の4kΩとしています.テール電流(IT)は式10で,ゲイン(Gd)は,式11で計算することができ,こちらも20dB(10倍)となっています.

・・・・・・・・・・・・・・・・・・・(10)

・・・・・・・・・・・・・・・・・・・(10)

・・・・・・・・・・・・・・・・(11)

・・・・・・・・・・・・・・・・(11)

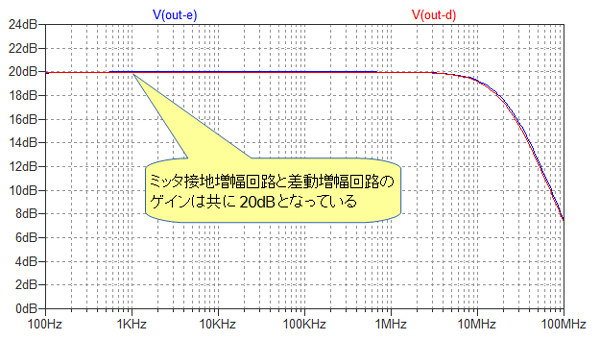

図6は,図5のシミュレーション結果です.エミッタ接地増幅回路と差動増幅回路(テール電流をエミッタ接地増幅回路の4倍)のゲインは,ともに20dBとなっています.

ミッタ接地増幅回路と差動増幅回路共にゲインは20dB

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice2_019.zip

●データ・ファイル内容

dif-amp.asc:図2の回路

CE-amp_dif-amp.asc:図5の回路

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs

(5) LTspiceアナログ電子回路入門・アーカイブs