抵抗1本の配置で,安定する回路はどっち?

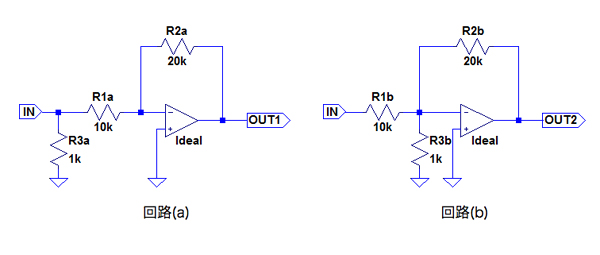

図1の回路(a)と(b)は,OPアンプを使用した反転増幅器です.回路の違いは抵抗(R3)の配置になります.回路(a)はIN(入力端子)とGND間にあり,回路(b)はOPアンプの反転端子とGND間にあります.信号ゲインを変えずに,ループ・ゲインを小さくすることで位相余裕が増し,安定する反転増幅器は回路(a)と(b)のどちらでしょうか.

ここで,OPアンプは,オープン・ループ・ゲインが100dBで,1st pole が100Hz,2nd pole が100kHzの理想OPアンプとします.

回路(a)は,R3aを入力端子とグランド間に配置した反転増幅器.

回路(b)は,R3bをOPアンプの反転端子とグランド間に配置した反転増幅器.

回路(b)

回路(a)は,INを接地すると,抵抗(R3a)の両端がGNDとなりR3aを無視することができます.その帰還率は,「R1a/(R1a+R2a)=1/3」となります.また,回路(b)は,INを接地すると「R1b」と「R3b」は並列接続となり,その帰還率は「(R1b//R3b)/(R2b+R1b//R3b)=1/23」になります.よって,帰還率の小さい回路(b)が,位相余裕が増し安定した回路となります.

●帰還率が小さいと位相余裕は増加し回路は安定する

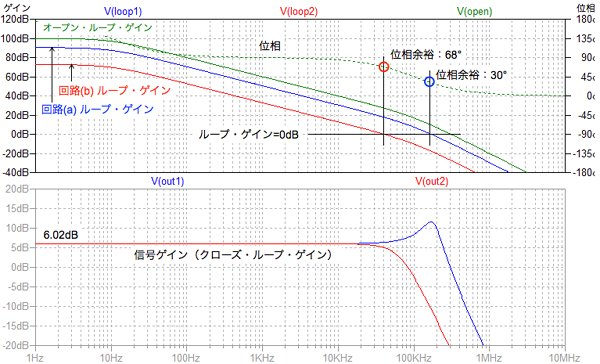

回路(a)と(b)のシミュレーション結果(図2)から,帰還率や位相余裕について解説します.まず,問題に,「信号ゲインを変えずに」とありますが,回路(a)の「R3a」は,IN端子とGND間に配置されています.そこで,INを接地すると,R3aは,信号電圧源の負荷抵抗になります.そのため,反転増幅器の信号ゲインには影響を与えません.また,回路(b)の「R3b」は, OPアンプの反転端子とGND間に配置されています.反転端子はバーチャル・グランドですので,信号電流は,R3bに流れず,負帰還のR1bとR2bに流れます.そのため,回路(b)も信号ゲインに影響を与えません.図2の下段を見ると1Hz~10kHz間で,回路(a)と(b)の信号ゲインは2倍(6.02dB)で変化していません.「|-R2/R1|=2倍」と同じであるが確認できます.

上段はOPアンプのオープン・ループ・ゲインと回路(a)と(b)のループ・ゲインの周波数特性と位相余裕.

下段は回路(a)と(b)の信号ゲインの周波数特性.

次に,図2の上段の回路(a)と(b)について,ループ・ゲインの周波数特性と位相余裕について解説します.回路(a)のINを接地すると,R3aの両端がGNDとなりR3aを無視できます.その帰還率は「R1a/(R1a+R2a)=1/3」です.同様に,回路(b)のINを接地するとR1bとR3bは並列接続となり,その帰還率は「(R1b//R3b)/(R2b+R1b//R3b)=1/23」になります.ここで二つの回路のOPアンプは同じであることから,オープン・ループ・ゲインは同じであり,位相特性は変わりません.帰還率は,周波数特性を持たない抵抗の減衰器であることから,回路(b)のループ・ゲインの周波数特性は,回路(a)に比べて,帰還率の差分だけ周波数特性のカーブが下にシフトします.

よって,帰還率が小さい回路(b)が位相余裕は68°となり,回路(a)の位相余裕30°と比べると,位相余裕が増加して回路は安定します.

●帰還率を小さくすると,状態が悪化する場合もある

回路(b)のように,反転増幅器はR3bを使用して,信号ゲインは変えずに,帰還率(β)を変更できます.ちなみに,非反転増幅器は信号ゲインと帰還率の逆数が同じ(信号ゲイン=1/β)なので,信号ゲインを変えずに,帰還率を変更できません.

信号ゲインを変えずに帰還率を変更する用途は,回路(b)のようにループ・ゲインの調整が挙げられます.しかし,帰還率を小さくすると,状態が悪化する特性もあります.例えば出力オフセット電圧の増加や出力雑音の増加など, 他の特性とのトレードオフが生まれます.このことから反転増幅器においてループ・ゲインを調整するときは,他の特性への影響を考慮しなければなりません.

そこで,他の特性への影響を解説するために,ここからは,OPアンプのマクロモデルを使用し,R3bによる帰還率の低下で位相余裕値が増加する様子と,過渡解析で発振が停止することを確かめます.またオフセット電圧を例にとり,そのトレードオフの関係を調べていきます.

●OPアンプのマクロモデルを使い反転増幅器をAC解析でシミュレーションする

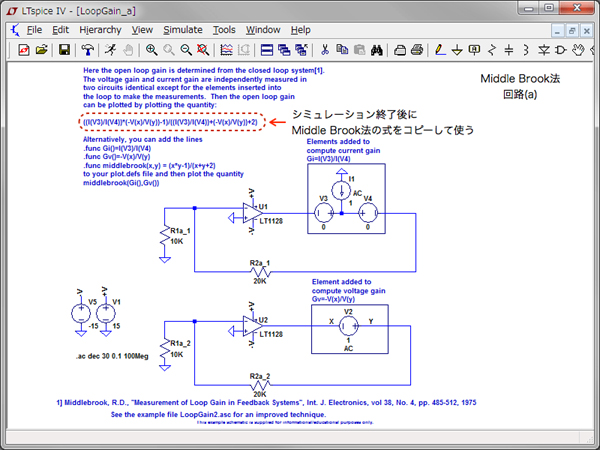

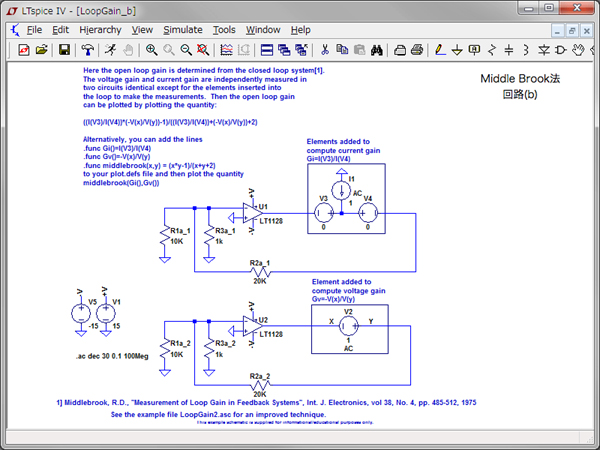

ループ・ゲイン周波数特性は,理論的に誤差のない測定手法の「middlebrook法」を使用します.middlebrook法は,Dr. R.David Middlebrookにより1975年に発表された真のループ・ゲインを得る手法です(1).LTspiceにはmiddlebrook法の実用例としてLTspiceインストール・ディレクトリの「Educational」フォルダに「LoopGain.asc」というファイル名で格納されています.Windows7 の環境では,「C:\Program Files\LTC\LTspiceIV\examples\Educational\LoopGain.asc」に格納されています.このLoopGain.ascを使用し回路図を編集します.

図3は,回路(a)のOPアンプをマクロモデル(LT1128)に変更し,ループ・ゲイン周波数特性を調べるシミュレーション回路です.

測定手法はmiddlebrook法を使用.

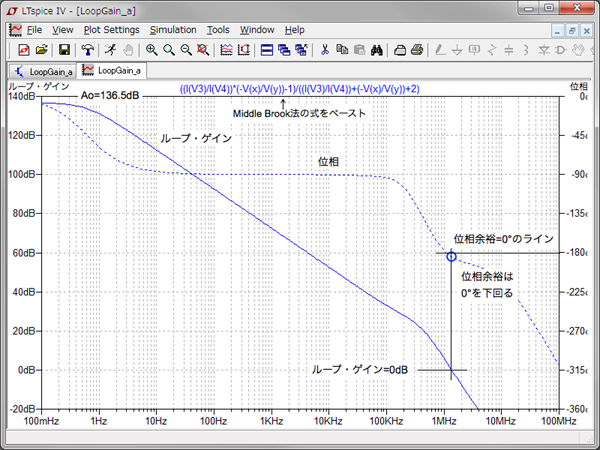

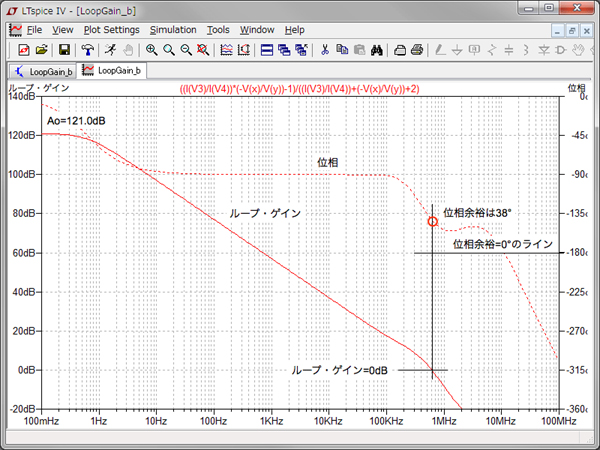

図4は,図3のシミュレーション結果で,図1の回路(a)に相当します.ループ・ゲインと位相の周波数特性より,位相余裕は0°を下回っており,負帰還は不安定であることから,発振すると考えられます.

同様に図5は,回路(b)のOPアンプをマクロモデル(LT1128)に変更し,ループ・ゲイン周波数特性を調べるシミュレーション回路です.

測定手法はmiddlebrook法を使用.

図6は,図5のシミュレーション結果で,図1の回路(b)に相当します.R3bにより,帰還率が小さくなるため,ループ・ゲインの周波数特性のカーブは,グラフ上で下にシフトしています.これより位相余裕は38°となり,回路(a)より回路(b)の方が 位相余裕を増すことができます.

ここで図3の帰還率(β)は「β=1/3」で,図5の帰還率(β)は「β=1/23」であることから回路(b)のループ・ゲインは,-17.7dB下方向へシフトする計算になりますが,そのようになっていません.図4と図6の100mHzでループ・ゲインの差を測ると-15.5dBです.また,位相のカーブも1MHz付近より高い周波数で差があります.これらは,OPアンプの入力インピーダンスが有限値で,かつ周波数特性を持つためです.

●位相余裕の差を過渡解析のシミュレーションで確かめる

次に過渡解析を用いて,時間軸での波形の差を調べます.R3bにより位相余裕を増していますので,その効果を調べるのが目的です.図7は,過渡解析を行うシミュレーション回路で,過渡解析は二つの回路へ,入力電圧を±100mV,立ち上がり時間と立ち下がり時間を1nsの矩形波を入力しました.

図8は,図7のシミュレーション結果で,上段が回路(a)で,下段が回路(b)です.回路(a)は,前述したようにAC解析で位相余裕が0°を下回り,負帰還は不安定な状態でした.この状態で,過渡解析を行うと位相余裕が0°付近の1.1MHzの周波数で出力端子は発振しています.回路(b)は,信号ゲインが2倍のままで,R3bによりループ・ゲインが下がり,結果として位相余裕が増していますので信号ゲインを変えずに発振が停止しています.これからもR3bの効果が分かります.

●トレードオフとなる特性の例「出力オフセット電圧」

R3bにより帰還率を小さくし,位相余裕を増すことはできました.しかし,この方法は出力オフセット電圧や出力雑音が増加するなど,ノイズ・ゲインに起因して状態が悪化します.これは帰還率を小さくするとその逆数であるノイズ・ゲインが高くなるためです.ここでは,R3bにより出力オフセット電圧がどの程度悪化するかを検討します.

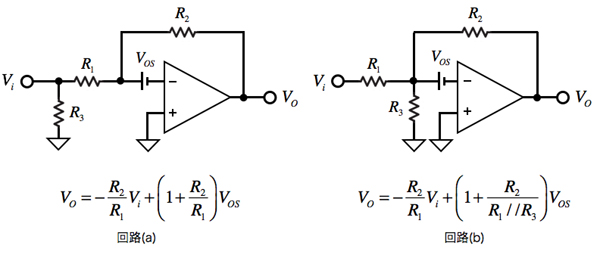

図9は,OPアンプの入力オフセット電圧(VOS)がある状態を示しています.図中に入力オフセット電圧がある時の出力電圧の式を掲載しました.二つの回路ともノイズ・ゲインにより入力オフセット電圧は増幅され,出力に現れることがわかります.これより,R3bにより帰還率を小さくすると,その逆数であるノイズ・ゲインが高くなり,出力オフセット電圧が増加します.

(a)は,回路(a)に入力オフセット電圧がある状態

(b)は,回路(b)に入力オフセット電圧がある状態 VOSは入力オフセット電圧

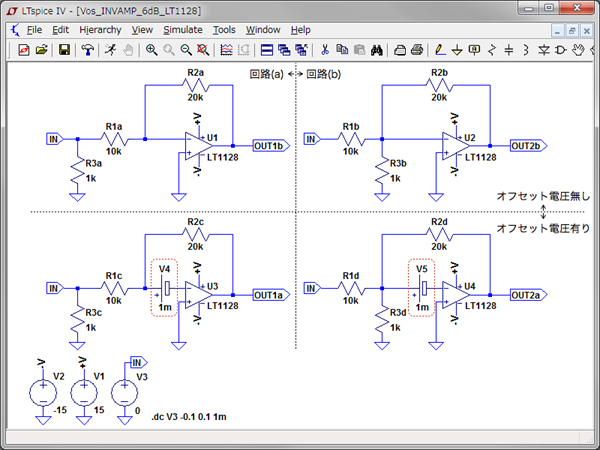

図10は,左が回路(a)で,右が回路(b)になります.また,上下で入力オフセット電圧1mVの有無とした,四つのシミュレーション回路です.四つの回路とも入力電圧は,-100mV~100mVを1mVステップで増加させています.

図中の左右で回路(a),回路(b)を分け,上下で入力オフセット電圧の有無の状態を示す.

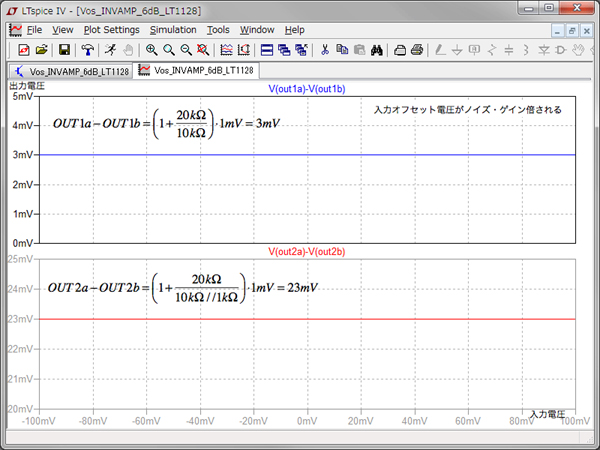

図11は,図10のシミュレーション結果で,入力オフセット電圧が有る回路から無い回路を減算し,出力オフセット電圧がいくら増えたか調べています.入力と出力の直流バイアス電圧が変わらない回路の方が良いのですが,結果は,回路(a)は3mVであるのに対し,回路(b)は23mVと増加しています.このように,帰還率を小さくするとその逆数であるノイズ・ゲインが高くなり出力オフセット電圧が増加し状態が悪化します.

出力オフセット電圧はノイズ・ゲインで増幅され出力に現れる.

ここでは計算しませんが,出力雑音電圧もノイズ・ゲインに関係することが多く,出力雑音は増加します.出力雑音とノイズ・ゲインの過去に配信したメルマガ「信号源抵抗が大きい回路でノイズが少ないプリアンプはどっち?」の図3を参照ください.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice033.zip

●データ・ファイル内容

LoopGain_a.asc:図3の回路

LoopGain_b.asc:図5の回路

Tran_INVAMP_6dB_LT1128.asc:図7の回路

VOS_INVAMP_6dB_LT1128.asc:図10の回路

※ファイルは同じフォルダに保存して,フォルダ名を半角英数にしてください

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs