位相余裕が安定ギリギリの45°になるI-V変換器はどっち?

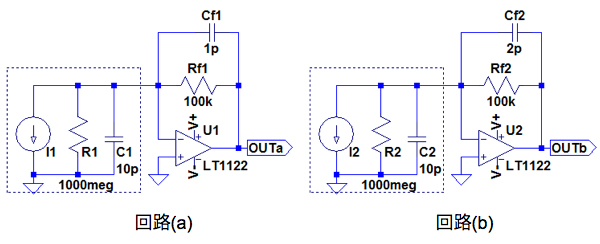

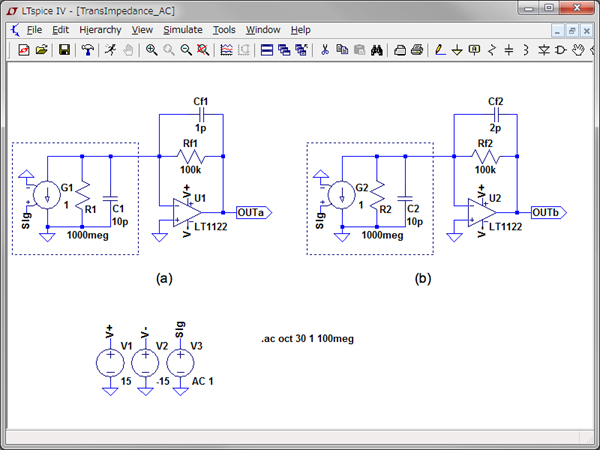

図1の回路(a)と(b)は,フォト・ダイオードからの電流信号を電圧に変換する電流-電圧変換器(I-V変換器)です.OPアンプは,GB積(ゲイン帯域幅積)が14MHzの製品を使用しています.フォト・ダイオードは,図の破線内で示すように,抵抗とコンデンサの等価回路で構成しています.二つの回路の違いは,負帰還回路のコンデンサ(Cf1,Cf2)の容量値が異なっています.このコンデンサの容量値で位相余裕が決まります.

一般的に,回路安定性を示す指標は,位相余裕が45°以上と言われていますが,回路(a)と(b)で,位相余裕が45°の回路はどちらでしょうか.

回路(a)と(b)の違いは,帰還回路のコンデンサ(Cf1,Cf2)の容量値が違っている.

回路(a)

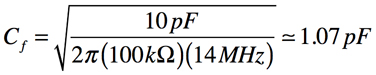

I-V変換器の位相余裕が45°の場合,負帰還回路の帰還容量(Cf)は,回路(a)と(b)の「Cf(10pF)」,「帰還抵抗Rf(100kΩ)」,「オペアンプのGB積f3(14MHz)」の三つの値から計算できます.計算式は,「Cf=√C1/2πRf1f3」となり「Cf=1.07pF」となります.これにより,回路(a)が位相余裕45°の回路となります.一方,回路(b)は位相余裕が45°よりも増え,回路(a)より負帰還は安定します.

●出力電流を電圧に変換するI-V変換器

I-V変換器は,入力電流に比例した出力電圧を得ることができ,フォト・ダイオードやD-Aコンバータ(DAC)の出力電流を電圧に変換する場合に使用されます.

まず,図1の回路(a)と(b)のI-V変換器をオペアンプと抵抗[帰還抵抗(Rf)],コンデンサ[帰還容量(Cf)]で構成するのかを解説します.

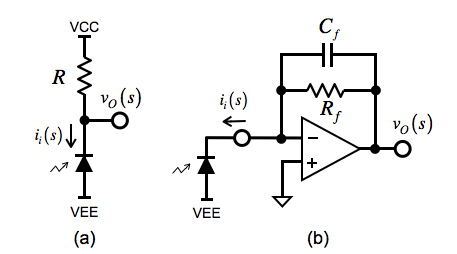

図2(a)は,フォト・ダイオードに照射された光量で生じた電流[ii(s)]を抵抗(R)のみで電圧に変換する例です.この回路は,電流[ii(s)]と抵抗(R)による電圧降下分だけ,出力電圧[vo(s)]も下がり,フォト・ダイオードの逆バイアス電圧も下がります.図2(a)の欠点は,フォト・ダイオードは,図1の等価回路に示したように,有限の出力抵抗(R1またはR2)を持ち,逆バイアス電圧の変化と出力抵抗により,フォト・ダイオードの電流[ii(s)]以外の誤差電流が発生します.

(a)抵抗1個で電圧に変換する例.

(b)I-V変換器で電圧に変換する例.

一方,図2(b)は,フォト・ダイオードに照射された光量で生じた電流[ii(s)]をI-V変換器により電圧に変換する例です.この回路は,帰還容量(Cf)のインピーダンスが帰還抵抗(Rf)に比べて十分大きい低周波帯の場合,帰還抵抗(Rf)により電圧に変換されます.この回路の場合,フォト・ダイオードに印加される逆バイアス電圧は,オペアンプのバーチャル・ショートの電圧で一定になり,図2(a)より誤差電流を抑えることができます.

I-V変換器に使用されるOPアンプは,入力バイアス電流が小さく,低雑音にするためJFET(Junction Field Effect Transistor)入力のOPアンプを使用します.雑音に関しては過去配信した「023 信号源抵抗が大きい回路でノイズが少ないプリアンプはどっち?」を参照してください.

●I-V変換器は帰還容量で負帰還の補償をする

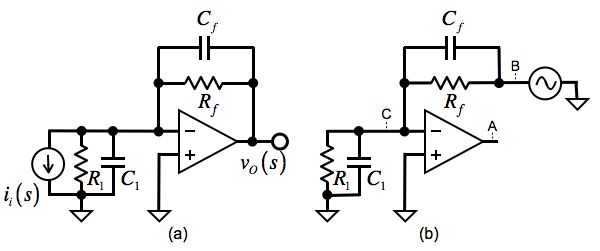

I-V変換器は,負帰還の補償として,帰還抵抗(Rf)と帰還容量(Cf)を並列に接続しなければ,不安定になります.不安定になる原因は,OPアンプの反転端子とフォト・ダイオードの接地間に「フォト・ダイオードの接合容量」,「配線の浮遊容量」,「OPアンプの入力容量」があるためです.図1の回路(a)と(b)のフォト・ダイオード等価回路の「C1とC2」はこれらの合算値になります.「C1とC2」による不安定な状態は,帰還容量(Cf)で補償されます.帰還容量(Cf)で補償される様子を図3(a)(b)で解説します.

図3(a)は,フォト・ダイオードを等価回路で表した「I-V変換器ゲイン[vo(s)/ii(s)]」を調べる回路です.図3(b)は,図3(a)の「ループ・ゲイン」,「オープン・ループ・ゲイン」,「ノイズ・ゲイン」を調べるために,ループを切った回路になります.ここでは,結果を分かりやすくするために,OPアンプは,直流のオープン・ループ・ゲインが120dBで,GB積が10MHzの理想オペアンプを使用しました.また,帰還容量(Cf)のインピーダンスが帰還抵抗(Rf)に比べて十分大きい低周波帯とするために「C1>Cf」,「R1>Rf」としています.

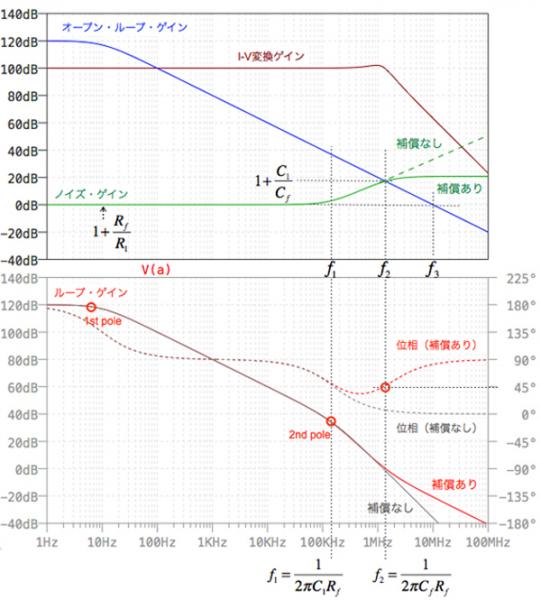

ここで,OPアンプのオープン・ループ・ゲインを「A(s)」,帰還率を「β(s)」,ノイズ・ゲインを「1/β(s)」とします.図3(b)の測定点「A」,「B」,「C」で説明すると,オープン・ループ・ゲインは「A/C」になります.ループ・ゲインは「A/B」となります.ノイズ・ゲインは「B/C」となります.これらをグラフにプロットしたものが図4になります.

図4上段で「補償なし」の破線は帰還容量(Cf)が無い場合です.図4下段で,帰還容量(Cf)が無い「位相(補償なし)」場合は,f2より高い周波数では位相余裕が0°で不安定です.負帰還の補償として,帰還容量(Cf)を入れることにより,f2の周波数でゼロ点を作り,「位相(補償あり)」のように位相を戻します.位相を戻している場合,f2は,位相余裕が45°を得られる周波数です.f2の周波数を図4上段でみると,f1の周波数(2nd poleになる周波数)から+20dB/decの傾きで上がり始めたノイズ・ゲインと,-20dB/decの傾きで下がるOPアンプのオープン・ループ・ゲインの交点であることが分かります.

●位相余裕を45°にする帰還容量を見積もる

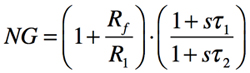

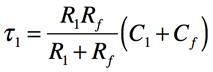

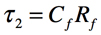

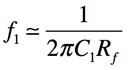

図4上段で示した位相余裕が45°になるf2は,帰還容量(Cf)で作ります.ここでは,その計算方法について解説します.まず,図4上下段のf1とf2を計算します.図3(b)の回路で,ノイズ・ゲインは式1となり,τ1(ノイズ・ゲインのゼロ点)は式2,τ2(ノイズ・ゲインのポール)は式3となります.τ1は「C1>Cf」,「R1>Rf」の場合,出力抵抗(R1)と帰還容量(Cf)が無視できます.f1は,式4で近似値が算出できます.次に,f2はτ2より式5となります.

ノイズ・ゲインは式1になります.

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

・・・・・・・・・・・・・・・・・・・・・・・・・(1)

τ1は式2.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・(2)

τ2は式3.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(3)

式4で近似値が算出できます.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(4)

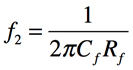

f2はτ2より式5となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(5)

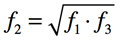

次にf2をf1,f3で表すと式6となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(6)

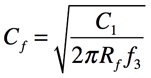

式5と式6よりCfは式7となります.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・(7)

位相余裕45°となる帰還容量(Cf)は,式7を使いC1,Rf,f3(ここでf3はOPアンプのGB積)の三つの値で計算できます.図1の回路(a)の三つの定数を式7に代入すると式8になり,位相余裕45°となる帰還容量(Cf)は1.07pFとなります.

・・・・・・・・・・・・・・・・・(8)

・・・・・・・・・・・・・・・・・(8)

次は,以上の結果をシミュレーションで確かめます.

●I-V変換器の特性をLTspiceで確かめる

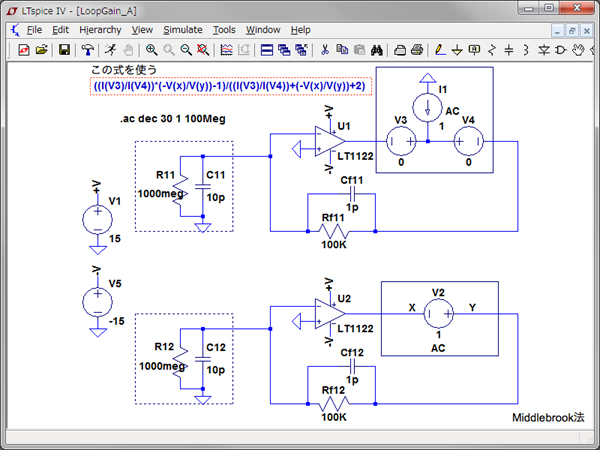

まず,図1の回路(a)と(b)のループ・ゲインと位相カーブから位相余裕を確認します.図5は,Middle Brook法で図1回路(a)のループ・ゲインと位相を調べる回路です.

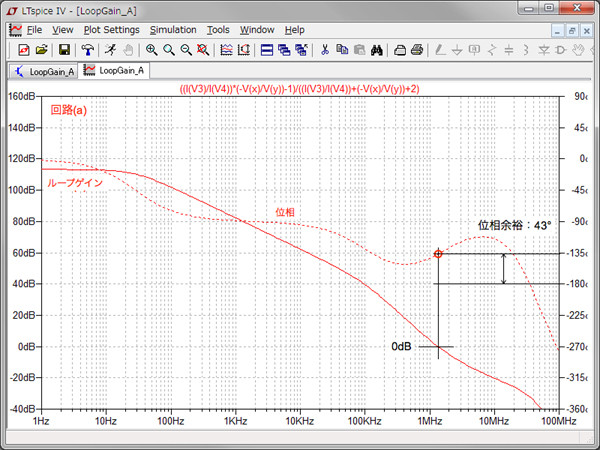

図6は,図5のシミュレーション結果となります.図6の位相余裕は43°であり,式8の値とほぼ等しいことがわかります.

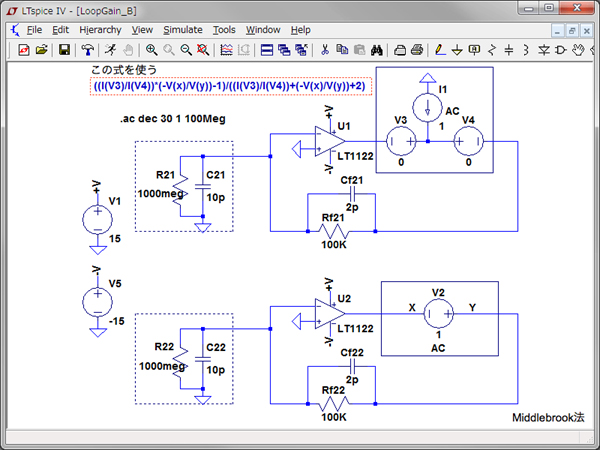

図7は,Middle Brook法で図1の回路(b)のループ・ゲインと位相を調べる回路です.

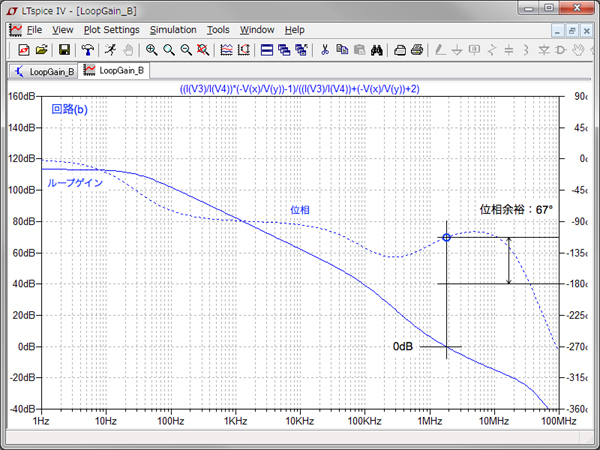

図8は,図7のシミュレーション結果です.図8は「Cf=2pF」の条件で位相余裕が67°あります.このように帰還容量(Cf)の値を大きくすると位相余裕が増えていきます.

図9は,図1の回路(a)と(b)のI-V変換ゲインを調べる回路です.

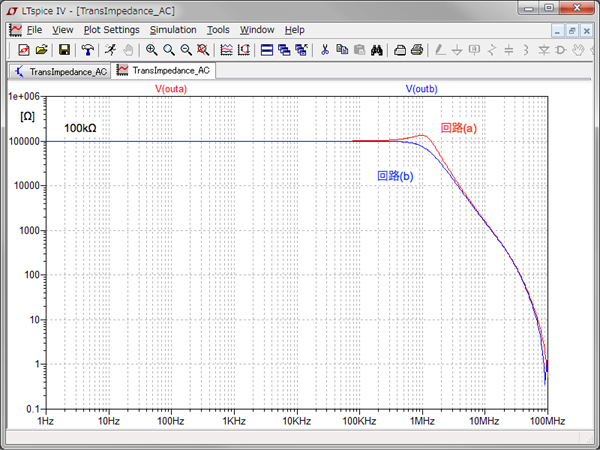

図10は,図9のシミュレーション結果です.I-V変換器ゲインの帯域幅は式5となります.式5を使った計算では,回路(a)が1.59MHzになり,回路(b)が796kHzになります.これらの値は,図10のシミュレーション結果と同じになっています.回路(a)のゲインにピークがあるのが位相余裕が43°のためです.

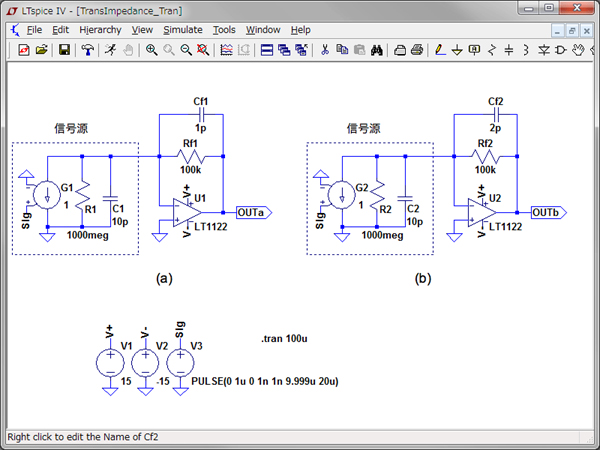

図11は,過渡解析で出力波形を調べる回路です.信号電流は1μAで,立ち上がり/立ち下がり時間が1nsで,50kHzの矩形波を入力しました.

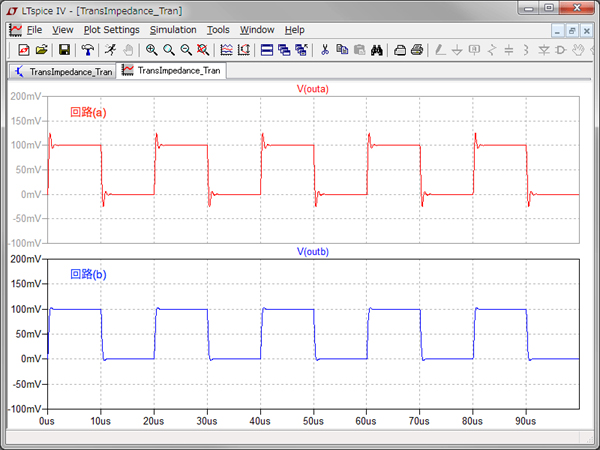

図12は,図11のシミュレーション結果です.図12上段[回路(a)で位相余裕が43°の場合]は,パルスの立ち上がりと立ち下がりで,オーバーシュートやアンダーシュートが出ています.また,図12下段[回路(b)で位相余裕が67°の場合]は,オーバーシュートやアンダーシュートは抑えられて.回路(a)に比べて安定しています.

●位相余裕の45°は回路安定の目安

I-V変換器の位相余裕を45°にする帰還容量(Cf)は計算で算出でき,これが設計する場合,一つの目安となります.ただし,位相余裕45°の場合は,I-V変換ゲインにピークがあり,過渡解析では,オーバーシュートやアンダーシュートが発生します.計算で求めた位相余裕を45°の帰還容量(Cf)を元に,シミュレーションのAC解析で位相余裕やゲイン余裕を確認し,過渡解析での波形を調べながら,回路定数を詰めていくのが良いでしょう.また,図11の過渡解析の回路で帰還容量(Cf)を削除すると,出力の発振する波形の様子が確認できますので,ぜひ試してください.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice043.zip

●データ・ファイル内容

LoopGain_A.asc:図5の回路

LoopGain_B.asc:図7の回路

TransImpedance_AC.asc:図9の回路

TransImpedance_Tran.asc:図11の回路

※ファイルは同じフォルダに保存して,フォルダ名を半角英数にしてください

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs