信号源抵抗が大きい回路でノイズが少ないプリアンプはどっち?

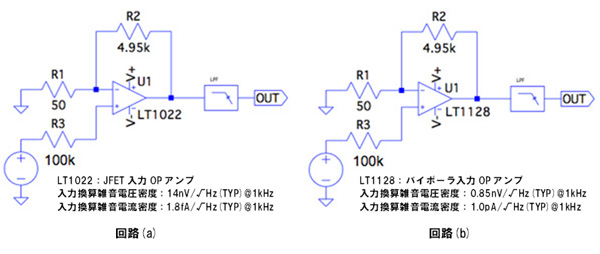

図1の回路(a)と(b)は,ともに回路定数は同じで,100kΩの大きな信号源抵抗(R3)を配置し,信号を100倍のゲインで増幅する非反転増幅器のプリアンプです.また,出力端子の手前に1次LPF(Low Pass Filter)があり,雑音帯域幅は5kHzで同じです.

回路の違いは,回路(a)はJFET(Junction Field Effect Transistor)入力のOPアンプ(LT1022)を使用し,回路(b)はバイポーラ入力のOPアンプ(LT1128)を使用しています.二つのOPアンプは,入力換算雑音電圧密度と入力換算雑音電流密度も違います.回路(a)と(b)で,OUT端子の全出力雑音電圧が小さい回路はどちらでしょうか?

回路(a)

大きな信号源抵抗からの信号を増幅する非反転増幅器のプリアンプは「入力換算雑音電流密度×信号源抵抗」が支配的になります.そこで,入力換算雑音電流密度が小さい特徴のJFET入力のOPアンプを選んだほうが,その全出力雑音電圧は小さくなります.

●信号源抵抗が大きな場合はJFET入力のOPアンプを選ぶ

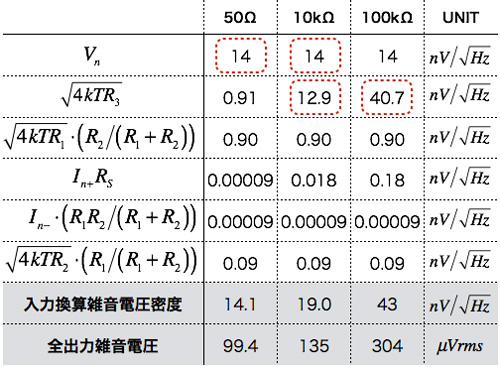

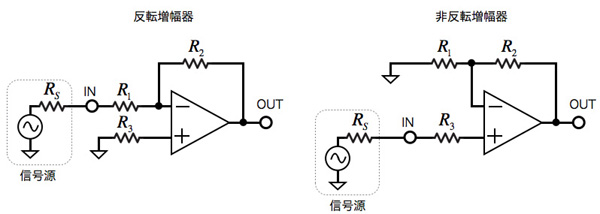

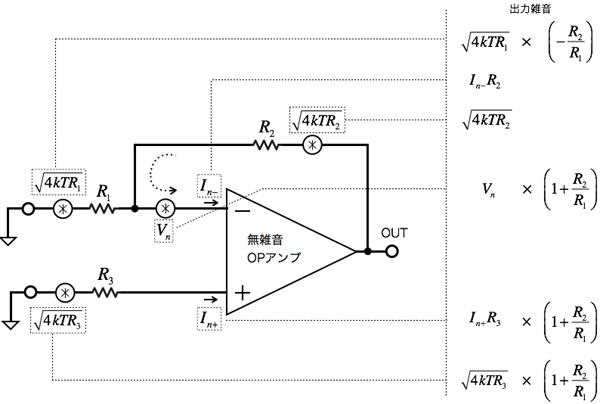

はじめに,算出した雑音電圧表で解答を簡単に解説します.回路(a)と(b)の雑音源は,六つあります.一つ目は,OPアンプの入力換算雑音電圧密度(Vn)です.二つ目は入力換算雑音電流密度(In+)で,三つ目は入力換算雑音電流密度(In-)です.あと三つの抵抗(R1,R2,R3)の熱雑音(√4kTR1,√4kTR2,√4kTR3)になります.

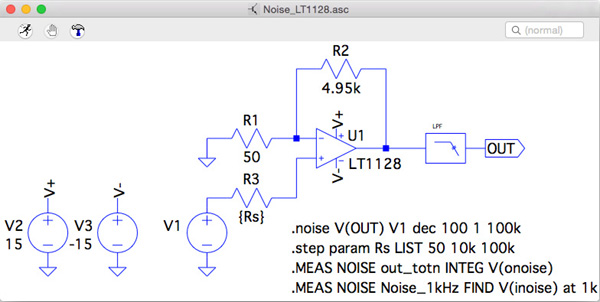

表1は,回路(a)のJFET入力OPアンプ(LT1022)を使用した場合の各雑音です.表2は,回路(b)のバイポーラ入力OPアンプ(LT1128)を使用した場合です.比較するために,それぞれ信号源抵抗(R3)を50Ω,10kΩ,100kΩとした時の各入力雑音電圧密度を載せました.赤枠は,各信号源抵抗の支配的な雑音電圧密度です.雑音は2乗和の平方根で計算することから仮に二つの雑音源の大小を比べた場合,3倍大きな雑音が支配的になります.

問題の回路(a)と(b)は,表1と表2の信号源抵抗が100kΩの場合を比較します.回路(a)のJFET入力OPアンプ(LT1022)の全出力雑音電圧は304μVrmsとなっています.回路(b)のバイポーラ入力OPアンプ(LT1128)の全出力雑音電圧は764μVrmsです.このように,信号源抵抗が大きな場合(100kΩ)では,JFET入力のOPアンプを選びます.入力換算雑音電流密度を小さくすることで,全出力雑音電圧を小さくできます.逆に信号源抵抗が小さな場合(50Ω)は,OPアンプの入力換算雑音電圧密度の小さいOPアンプを使用したほうが,全出力雑音電圧は少なくなります.

●低雑音プリアンプの設計は,支配的な雑音項目を見極める

OPアンプ入力段の差動増幅器へ使用するデバイスは,JFETやバイポーラ,CMOSがあります.このデバイスの違いにより,入力バイアス電流に大小があります.JFETやCMOSの入力バイアス電流は,バイポーラに比べて非常に小さな値です.一般にJFET入力のOPアンプの入力換算雑音電圧密度は数十nV/Hz1/2で,入力換算雑音電流密度は数fA/Hz1/2です.バイポーラ入力のOPアンプは,入力換算雑音電圧密度が1nV/Hz1/2~数十nV/Hz1/2で,入力換算雑音電流密度は数pA/Hz1/2です.

低雑音のプリアンプを設計するときは,どの雑音の項目が支配的かを見極めながら進めます.信号源抵抗が大きなときは,入力換算雑音電圧密度より「入力換算雑音電流密度×信号源抵抗」に配慮しなければ低雑音になりません.

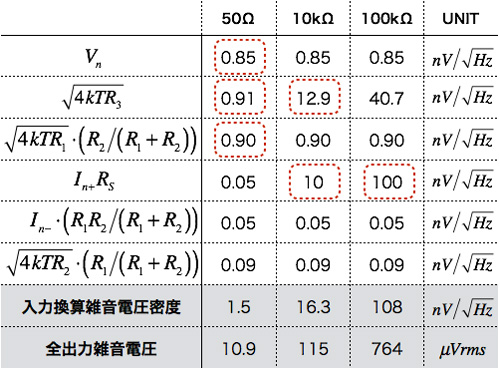

●プリアンプは非反転増幅器が使用される

図2に示すようにOPアンプを使った増幅器は,反転増幅器と非反転増幅器があります.プリアンプは非反転増幅器が使用されます.理由としては,プリアンプのR1は,大きくすると雑音が増すため,低雑音にするにはR1を小さな値にしなければなりません.また,反転増幅器の場合,OPアンプは反転端子がバーチャル・グラウンドなので,入力インピーダンスはR1となります.したがって,出力インピーダンス(RS)と入力インピーダンス(R1)で信号が減衰しますので,プリアンプは,入力インピーダンスが大きな非反転増幅器が使用されます.

プリアンプは非反転増幅器が使用される

●全出力雑音電圧を求める

図3の回路は,雑音を計算する回路です.図3は,図2の反転増幅器と非反転増幅器の信号源を外し,IN端子をGNDへ接続した回路です.OUT端子の全出力雑音電圧を求める場合,図3と図2は,同じになります.なので,抵抗値とOPアンプが同じなら,反転増幅器でも非反転増幅器でも全出力雑音は同じになります.

全出力雑音電圧を非反転増幅器の増幅率(1+R2/R1)で除算したものが入力換算雑音電圧です.非反転増幅器の増幅率(1+R2/R1)はノイズ・ゲインと呼ばれ,反転増幅器や非反転増幅器の両方の雑音解析に使用します.

出力に現れる六つの雑音を示した

●雑音の和は2乗和の平方根

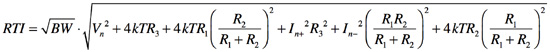

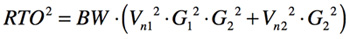

図3のOUT端子の全出力雑音電圧から,ノイズ・ゲインを使用して,入力換算雑音電圧を求めます.雑音源は,OPアンプの入力換算雑音電圧密度(Vn)と入力換算雑音電流密度(In+,In-),あと三つの抵抗の熱雑音(√4kTR1,√4kTR2,√4kTR3)の合計六つです.図3の右側にある式は六つの雑音源によって出力に現れる雑音電圧を記載しました.雑音の和は,単なる加算ではなく,2乗和の平方根で計算します.入力換算雑音電圧(RTI:Referred to The Input)は,六つの雑音をノイズ・ゲインで除算し2乗和の平方根で計算したものですので式1となります.

・・・・・(1)

・・・・・(1)

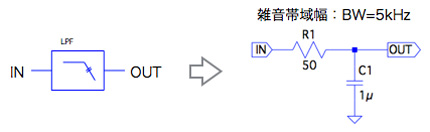

ここでBWは雑音帯域幅であり,回路(a)と(b)の1次LPF(図4)で与えられます.1次LPFのカットオフ周波数(fc)と雑音帯域幅の関係は「BW=fc×π/2 」です.雑音帯域幅については「雑音が少ない1次ロー・パス・フィルタはどっち?」を参照ください.

雑音帯域幅:BW=5kHz

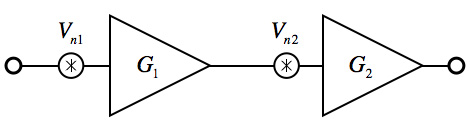

●縦続接続した回路の入力換算雑音電圧

問題の図1には,非反転増幅器の後段に図4の1次LPFを縦続接続しています.LPFには50Ωの抵抗があり,これも熱雑音を発生しますが,縦続接続した全体の入力換算雑音電圧(RTI)は,その2段目以降の雑音(ここではVn2)が前段までのゲイン(ここではG1)で除算した値に見えるため前段までのゲインが大きいと無視できます.

図5は,2段の縦続接続回路を現しています.G1は初段増幅器のゲインで,Vn1は初段増幅器の入力換算雑音電圧,G2は2段目増幅器のゲインで,Vn2はその入力換算雑音電圧です.

G1は初段増幅器のゲイン, Vn1は初段増幅器の入力換算雑音電圧,G2は2段目増幅器のゲイン,Vn2はその入力換算雑音電圧

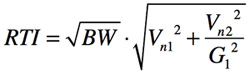

出力に現れる雑音電圧をRTO (Referred to The Output)とすると式2のように表せます.全体回路の入力換算雑音電圧はRTOをゲイン(G1*G2)で除算したしたものですから式3になります.2段目の雑音Vn2は,前段までのゲイン(G1)で除算された値に見えます.1次LPFの50Ωは,図1のR1と同じ熱雑音ですが,この理由により無視でき,回路(a)と(b)ともに,式1から雑音を求めることができます.

・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・(2)

・・・・・・・・・・・・・・・・・・・・・・・・・(3)

・・・・・・・・・・・・・・・・・・・・・・・・・(3)

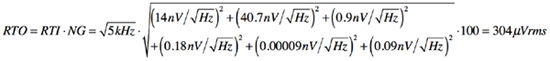

以上より,図1の回路(a)の全出力雑音(RTO)は,ノイズ・ゲインを「NG=1+R2/R1=100」とすると式4になり

・・・・・(4)

・・・・・(4)

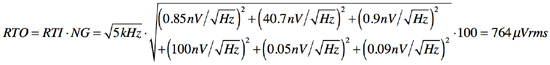

同様に, 回路(b)は式5となります.

・・・・・(5)

・・・・・(5)

これより信号源抵抗が100kΩの場合,JFET入力のOPアンプのほうが出力に現れる雑音は小さくなります.

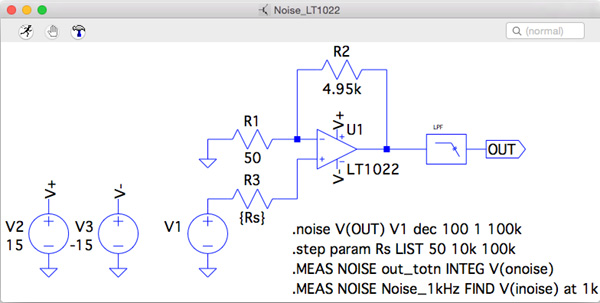

●LTspiceで雑音をシミュレーションする

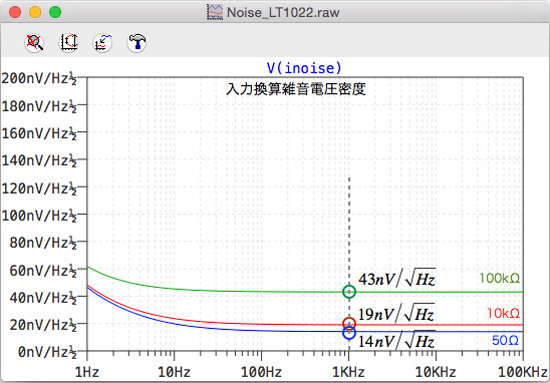

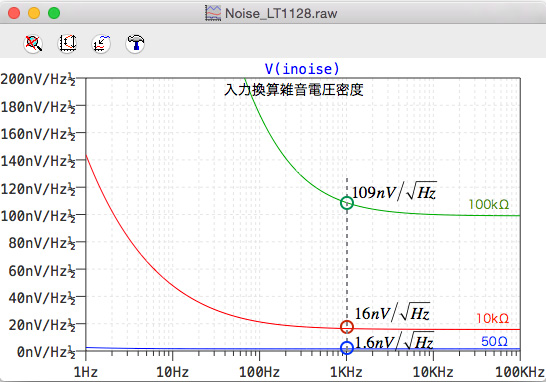

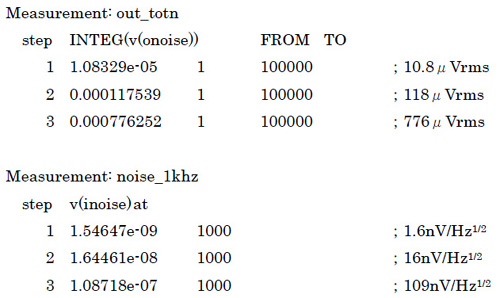

図6は,回路(a)のJFET入力のOPアンプ(LT1022)を使用した雑音をシミュレーションする回路です.図7は,その結果となります.比較のために信号源抵抗値は,変数(RS)として50Ω,10kΩ,100kΩの3種を「.step」コマンドを使用して変えています.

カーソル機能で雑音を測るが大変なので, 「.MEAS」コマンドを使用して出力に現れる全出力雑音と1kHz時の入力換算雑音電圧密度を探し出し,それらを1回のシミュレーションで得られるようにしました.

全出力雑音電圧はLTspiceの文法から「.MEAS NOISE out_totn INTEG V(onoise)」となり,内容は「NOISE解析において,全出力雑音電圧を変数out_totnへ入れなさい」となります. V(onoise)は,「.noise」で指定した出力,ここではVOUTの全出力雑音電圧です.

1kHz時の入力換算雑音電圧密度は,LTspiceの文法から「.MEAS NOISE Noise_1kHz FIND V(inoise) at 1k」となり,内容は「NOISE解析において,1kHz時の入力換算雑音電圧密度を探し出し,変数Noise_1kHzへ入れなさい」となります.V(inoise)は,「.noise」で指定した入力で,ここではV1部分の入力換算雑音電圧密度です.

「.MEAS」コマンドの結果はログ・ファイルに記録されます. ログ・ファイルを見るときはメニューバの「View > SPICE Error Log」または, ショートカット・キーの「Ctrl+L」でログ・ファルのウィンドが現れます.

「.MEAS」でログ・ファイルに記録された回路(a)の雑音

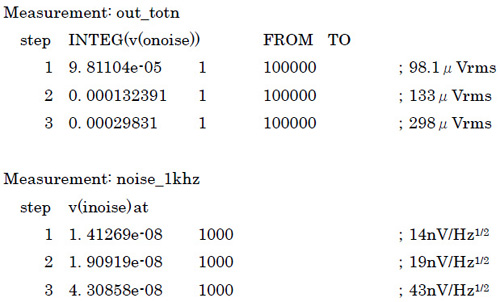

同じように,図8は,回路(b)のバイポーラ入力のOPアンプ(LT1128)を使用した回路で,図9はその結果となります.

「.MEAS」でログファイルに記録された回路(b)の雑音

ログ・ファイルに記録された1kHz時の入力換算雑音電圧密度は,表1,表2とほぼ同じです.全出力雑音電圧は低周波の1/f雑音が加わるため僅かに差がありますが,計算値に近い値であることが確かめられました.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice023.zip

●データ・ファイル内容

LPF.asc:図4の1次LPF回路

LPF.asy:図4の1次LPFシンボル

Noise_LT1022.asc:図6の回路(a)JFET入力OPアンプ(LT1022)を使用した回路

Noise_LT1128.asc:図8の回路(b)バイポーラ入力OPアンプ(LT1128)を使用した回路

※ファイルは同じフォルダに保存して,フォルダ名を半角英数にしてください

■LTspice関連リンク先

(1) LTspice ダウンロード先

(2) LTspice Users Club

(3) トランジスタ技術公式サイト LTspiceの部屋はこちら

(4) LTspice電子回路マラソン・アーカイブs